# A Reconfigurable ATM Transmitter/Receiver Implementation

C.N. Gupta Joseph B. Evans Gary J. Minden

TISL Technical Report TISL-9770-30

Prepared for:

Defense Advanced Research Projects Agency/CSTO

Research on Gigabit Gateways AARPA Order No. 8634 Issued by EDS/AVS under Contract #F19628-92-C-0080

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the U.S. government.

August 1993

Telecommunications and Information Sciences Laboratory

The University of Kansas Center for Research, Inc.

2291 Irving Hill Drive Lawrence, Kansas 66045

#### Abstract

An architecture to perform principal receive and transmit functions in a B-ISDN network is presented in this report. This innovative design can be reconfigured to function as a single STS-12c channel or four independent STS-3c channels. The design has been mapped on Field Programmable Gate Arrays (FPGAs). The transmitter chips accept ATM cells from the data source, perform ATM cell scrambling and map the ATM cells into a SONET frame. For the 4xSTS-3c case, the transmitter also byte interleaves the four channels. The receiver performs ATM cell delineation, discards idle cells and descrambles ATM cells. For the 4xSTS-3c case, it de-interleaves the four channels before storing the words into an SRAM. The potential problems in implementing ATM layer functions for higher rate STS signals are analyzed.

# **Contents**

| 1 | Intr | roduction                                             | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Organization of the report                            | 3  |

| 2 | Bac  | kground                                               | 4  |

|   | 2.1  | B-ISDN Protocol Reference model                       | 4  |

|   | 2.2  | A review of SONET                                     | 5  |

|   |      | 2.2.1 An overview of ATM                              | 7  |

|   | 2.3  | ATM Delineation                                       | 8  |

|   | 2.4  | The AN2 ATM Switch                                    | 9  |

|   | 2.5  | The Gateway Card                                      | 1  |

|   |      | 2.5.1 Transmit Section                                | 2  |

|   |      | 2.5.2 Receive Section                                 | 4  |

|   |      | 2.5.3 The Line Card Processor                         | 6  |

|   | 2.6  | Xilinx FPGAs                                          | 6  |

| 3 | Tra  | nsmitter Architecture 1                               | 7  |

|   | 3.1  | Functionality specifications                          | 9  |

|   | 3.2  | Architecture for the STS-12c mode                     | 20 |

|   |      | 3.2.1 Datapath of Transmitter Chip1                   | 20 |

|   |      | 3.2.2 State machine for STS-12c Chip1                 | 26 |

|   |      | 3.2.3 Transmitter Chip2 design for the STS-12c mode 2 | 27 |

|   | 3.3 | Design  | n for the 4 x STS-3c mode                                 | 29 |

|---|-----|---------|-----------------------------------------------------------|----|

|   |     | 3.3.1   | Data path design for the first transmitter chip           | 29 |

|   |     | 3.3.2   | State machine for the 4 x STS-3c Chip1                    | 32 |

|   |     | 3.3.3   | Design of the second transmitter chip for 4 x STS-3c mode | 33 |

|   | 3.4 | Design  | n for the STS-12c transmitter using 51.44 ns clock        | 38 |

|   | 3.5 | Design  | n for 4 x STS-3c transmitter using 51.44 ns clock         | 42 |

|   | 3.6 | Summ    | nary                                                      | 44 |

| 4 | Rec | eiver 1 | Architecture                                              | 45 |

|   | 4.1 | Functi  | ions of ATM Delineators                                   | 47 |

|   | 4.2 | Archit  | tecture for the STS-12c mode                              | 48 |

|   |     | 4.2.1   | Datapath of ATM Delineator Chip1                          | 48 |

|   |     | 4.2.2   | State Machine for Chip1                                   | 53 |

|   |     | 4.2.3   | Chip2 Datapath                                            | 55 |

|   |     | 4.2.4   | State machine for Chip2                                   | 56 |

|   | 4.3 | Archit  | tecture of the 4 x STS-3c mode                            | 60 |

|   |     | 4.3.1   | Datapath of 4 x STS-3c delineator Chip1                   | 60 |

|   |     | 4.3.2   | State machine for Chip1                                   | 63 |

|   |     | 4.3.3   | Chip2 Datapath for the 4 x STS-3c mode                    | 65 |

|   |     | 4.3.4   | State machine for Chip2                                   | 70 |

|   | 4.4 | Design  | n for the STS-12c receiver using 51.44 ns clock           | 73 |

|   | 4.5 | Summ    | nary                                                      | 78 |

| 5 | Per | formar  | nce Scalability in ATM Networks                           | 79 |

|   | 5.1 | Analy   | sis of the ATM Receiver                                   | 79 |

|   |     | 5.1.1   | Constraints                                               | 82 |

|   |     | 5.1.2   | Analysis of ATM Cell Delineation                          | 83 |

|   |     | 5.1.3   | Analysis of Idle Cell Detection Logic                     | 87 |

|   |     | 5.1.4   | Analysis of ATM Descrambler                               | 88 |

•

|              |             | 5.1.5 Results for the ATM Receiver                     | 88  |

|--------------|-------------|--------------------------------------------------------|-----|

|              | 5.2         | Analysis of the ATM Transmitter                        | 90  |

|              |             | 5.2.1 Analysis of ATM Scrambler                        | 92  |

|              |             | 5.2.2 Results for the ATM Transmitter                  | 94  |

|              | 5.3         | SONET Considerations                                   | 96  |

|              | 5.4         | AAL-5 Considerations                                   | 97  |

|              | 5.5         | Conclusion and Discussion                              | 101 |

| 6            | Con         | clusions                                               | 103 |

| A            | oc.         | 12c Transmitter                                        | 115 |

|              | <b>A.</b> 1 | Behavioral model of OC-12c transmitter: Chip1          | 115 |

|              | A.2         | Behavioral model of OC-12c transmitter: Chip2          | 123 |

|              | A.3         | Simulation results for OC-12c transmitter              | 125 |

|              | A.4         | OC-12c Transmitter Chip1 FPGA Layout                   | 127 |

|              | A.5         | OC-12c Transmitter Chip2 FPGA Layout                   | 129 |

| В            | 4 x         | OC-3c Transmitter                                      | 146 |

|              | B.1         | Behavioral model of 4xOC-3c transmitter: Chip1         | 146 |

|              | <b>B.2</b>  | Behavioral model of 4xOC-3c transmitter: Chip2 $\dots$ | 155 |

|              | B.3         | Simulation results for 4xOC-3c transmitter             | 158 |

|              | <b>B.4</b>  | 4xOC-3c Transmitter Chip1 FPGA Layout                  | 160 |

|              | B.5         | 4xOC-3c Transmitter Chip2 FPGA Layout                  | 162 |

| C            | OC-         | 12c Transmitter and Receiver Simulation                | 164 |

| D            | 4xO         | C-3c Transmitter and Receiver Simulation               | 166 |

| $\mathbf{E}$ | OC-         | 12c Receiver                                           | 174 |

|              | E.1         | Behavioral model of OC-12c receiver: Chip1             | 174 |

|              | E.2         | Schematics of OC-12c Receiver: Chin1                   | 170 |

|              | <b>E.3</b> | Behavioral model of OC-12c receiver: Chip2                | 184 |

|--------------|------------|-----------------------------------------------------------|-----|

|              | <b>E.4</b> | Schematics of OC-12c Receiver: Chip2                      | 188 |

|              | E.5        | OC-12c receiver Chip1 FPGA Layout                         | 190 |

|              | E.6        | OC-12c receiver Chip2 FPGA Layout                         | 192 |

| F            | 4 x        | OC-3c Receiver                                            | 196 |

|              | F.1        | Behavioral model of 4xOC-3c receiver: Chip1               | 196 |

|              | F.2        | Schematics of 4xOC-3c Receiver: Chip1                     | 200 |

|              | F.3        | Behavioral model of 4xOC-3c receiver: Chip2               | 204 |

|              | F.4        | Schematics of 4xOC-3c Receiver: Chip2                     | 207 |

|              | F.5        | 4xOC-3c receiver Chip1 FPGA Layout                        | 209 |

|              | F.6        | 4xOC-3c receiver Chip2 FPGA Layout                        | 211 |

| $\mathbf{G}$ | oc-        | -12c Receiver using 51.44 ns clock                        | 214 |

|              | G.1        | Simulation results of the receiver                        | 214 |

|              | G.2        | FPGA layout of the OC-12c receiver: Chip1                 | 216 |

|              | G.3        | State machine of the OC-12c receiver using 51.44 ns clock | 217 |

| н            | Sin        | nulation results of the ATM receiver connected to Receiv  | e   |

| Βı           | ıffer      | Controller                                                | 224 |

|              | H.1        | Simulation results for OC-12c mode                        | 224 |

|              | H.2        | Simulation results for 4 x OC-3c mode                     | 227 |

# Chapter 1

# Introduction

The architecture of the international telecommunications infrastructure is undergoing a change from dedicated transmission facilities toward high-bandwidth virtual channel facilities that are reconfigured. This change is brought about by the introduction of Broadband ISDN (B-ISDN). The emerging B-ISDN networks enable a variety of services, such as video teleconferencing, multimedia communication systems and still-image transmission systems. These new applications have large bandwidth requirements and delay sensitivities that cannot be supported by the existing networks. The emerging demand for multimedia and broadband services and the desire to integrate these future services on a single type of user network interface have prompted a focused effort to define B-ISDN standards. The standards bodies recommend a standardized transport, multiplexing and switching technology called Asynchronous Transfer Mode (ATM) as the basis for B-ISDN. ATM uses small cells, allowing efficient multiplexing of continuous and bursty traffic. ATM provides the flexibility for providing bandwidth on demand. The potential of ATM based networks has prompted all the major public carriers in Japan, Europe and United States to move toward ATM cell based networks [9][12].

Traditionally, computer networks can be divided into Local Area Networks

(LAN) and Wide Area Networks (WAN). LANs are used to interconnect computers a few miles apart. WANs interconnect computers across wide geographical spans. The use of similar technology in LAN and WAN environments based on B-ISDN provides the opportunity for geographically distributed high performance networks. Fiber has emerged as the transmission technology, since it can provide the required bandwidth. The transmission of digital information over optical fiber is covered in the standards for Synchronous Optical NETwork (SONET). The standard defines a new hierarchy, that is, a new set of common rates and formats that capitalize on the capabilities of an optical fiber transmission network. The possibility of new services has lead both exchange carriers and computer network providers to embrace technologies such as SONET and particularly ATM for both local and wide area networks. The new formats are more robust compared to the existing protocols and as a result are more complex to implement. For instance, processing SONET STS-12c requires a circuit in which at least a small portion operates at 622 Mb/s. Most parts of the circuit can operate at a much lesser frequency by operating on data in parallel. But, there are limitations on parallelizing the data.

Gateways, which interface LANs with WANs, play a key role in the realization of high performance distributed networks. The work presented here is a part of a gateway that interfaces an AN2 LAN with the MAGIC backbone network. The AN2 is a LAN based on ATM technology, developed by Digital's Systems Research Center. The Multi-Applications and Gigabit Internetwork Consortium, MAGIC is one of the six gigabit wide area testbeds being created for research in high speed networks. MAGIC is a group of industrial, academic, and government organizations participating in gigabit network research. The MAGIC backbone will span approximately 1000 kilometers and will operate at 2.4 Gb/s. The gateway provides a 622 Mb/s connection between the LAN and WAN environments, and supports either a single STS-12c or four STS-3c tributaries. The AN2 LAN

and the gateway are described in Chapter 2. The transmission rate for STS-12c is 622 Mb/s and is 155 Mb/s for each STS-3c stream.

# 1.1 Organization of the report

This work presents an architecture developed to perform the ATM functions of the B-ISDN protocol reference model in the gateway card. Two circuits are presented, one for a single STS-12c channel and another for four STS-3c channels.

The designs have been implemented using Xilinx Field Programmable Gate Arrays (FPGAs). Field programmable gate arrays have the advantage that they can be reprogrammed easily without removing them from the card. Both of the designs use the same hardware resources and hence the network can be reconfigured. The next chapter gives some background on the B-ISDN protocol reference model. The physical layer, i.e SONET, and the ATM layer of the model are described. Some background material on the AN2 ATM switch and the gateway card are then described. The subsequent chapter describes the STS-12c and the 4 x STS-3c transmitter architectures. Following that, the receiver architectures are described. An analysis of the scalability of ATM and SONET is performed in Chapter 5. The purpose of this analysis is to derive the implementation requirements for higher rate STS signals. Finally, the conclusions are presented.

# Chapter 2

# Background

## 2.1 B-ISDN Protocol Reference model

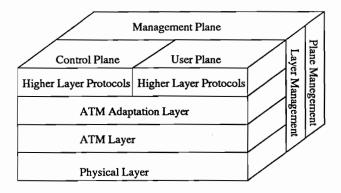

The B-ISDN protocol reference model is analogous to the OSI model of the International Standards Organization (ISO) [14]. The B-ISDN model, shown in Figure 2-1, has been widely used to model a wide variety of communication systems [11].

Figure 2-1: B-ISDN Protocol Reference Model

The model uses the concept of separated planes for the segregation of user, control, and management functions [6]. The user plane, with its layered structure, provides for user information flow along with associated controls. The control plane deals with the signaling functions necessary for call and connection setup, supervision and release. The management plane provides plane management and

layer management functions. The user and the control planes have layered structures. The physical layer is based on SONET transmission standards, which is described below. The ATM layer and the AAL layer roughly correspond to layer 2 of the OSI model. The role of the ATM layer is to transport the ATM cells and is common to all services. The ATM layer performs multiplexing and demultiplexing of cells of different connections, translation of VCI and VPI, passing of cell information to and from the ATM Adaptation Layer (AAL), and flow control and policing functions at the UNI. The function of the AAL is to adapt the various applications to the ATM layer.

### 2.2 A review of SONET

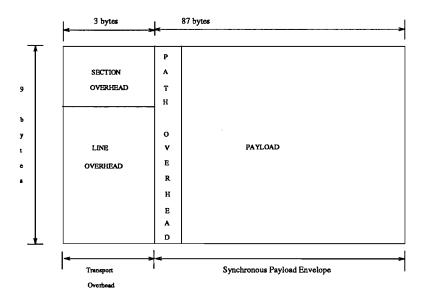

The basic building block of the SONET format is the Synchronous Transport Signal (STS-1) [22]. The STS-1 frame consists of an overhead portion and a payload portion. The overhead is broken into three parts: path, line and section overhead, as shown in Figure 2-2.

Figure 2-2: SONET STS-1 Frame Format

The Synchronous Payload Envelope (SPE) is the area reserved for transporting the payload, and contains 783 bytes per frame. Nine bytes in the SPE are overhead information that the system uses to verify the integrity of the payload and to supply end-to-end signaling. These nine bytes of overhead are referred to as Path overhead and they stay with the payload until it reaches its final destination. The remainder of the STS-1 frame consists of twenty-seven bytes, used for internetwork signaling and error checking. Nine bytes of the twenty-seven are used for the section portion of the network, that is, between optical repeaters. The remaining eighteen bytes are used for the line portion of the network, that is, between terminals. The first three bytes of every frame contain the frame word (two bytes) and the channel identification byte. The entire STS-1 frame consists of 810 bytes. It repeats at 125  $\mu$ s intervals, giving a nominal bit rate of 51.84 Mb/s.

Synchronous Transport Signals can be multiplexed into higher level signals denoted by the terminology STS-N, where N denotes the number of STS-1's that have been byte multiplexed together. The equivalent optical signal of STS-N is given the designation OC-N. Higher rate signals can be achieved by concatenation of individual STS-1 frames in a single STS-Nc frame.

SONET networks use a pointer to do frequency and phase aligning of the payload. These pointers are similar to the software pointers. The SONET pointer contains the location of the beginning of the data payload. The payload is allowed to move forward or backward within the frame. Transmission of the STS frames is done row by row, from left to right.

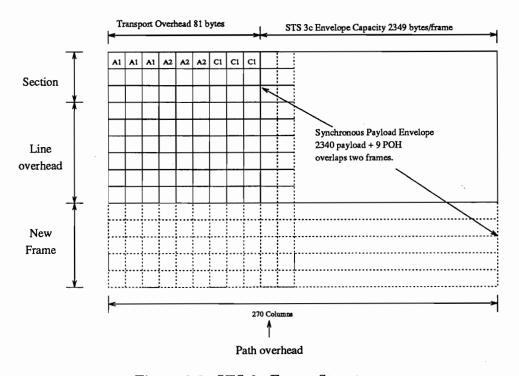

A SONET STS-3c is a concatenated STS-3 and carries a single stream. Figure 2-3 shows the SONET STS-3c frame. It is a 2430 byte pattern that repeats every  $125\mu s$ . Transmission is row by row, from left to right. Its two main components are the 81 byte Transport Overhead (TOH) and the 2349-byte Synchronous Payload Envelope (SPE). STS tributary multiplexing is a process in which the transport

overhead of the tributary signals are frame aligned, and in which the tributary signals are sequentially byte-interleaved. This results in the the appearance of the byte triplets A1,A2,C1, etc. in the STS-3c frame, even though the STS-3c is not itself created by tributary multiplexing. Bytes A1 and A2 form a framing pattern which identifies the beginning of each frame. Some of the overhead bytes in an STS-3c, such as the path overhead byte, are defined only for the first STS-1 position in the concatenated structure.

Figure 2-3: STS-3c Frame Structure

An STS-3c stream is at thrice the basic SONET rate, that is at 155.52 Mb/s. STS-12c is a single stream at 622 Mb/s.

#### 2.2.1 An overview of ATM

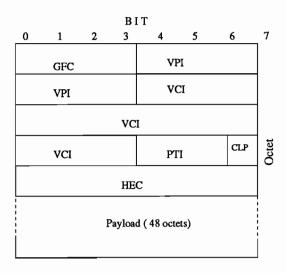

ATM is the target technology for the implementation of the services offered by Broadband ISDN [3]. ATM cells are fixed-size data units consisting of a header (5 bytes) and body (48 bytes), as shown in Figure 2-4. The header contains a *Virtual*

Circuit Identifier (VCI) and a Virtual Path Identifier (VPI) which are used for routing. The PTI field contains the Payload Type Indicator. The PTI is used by AALs. The CLP field indicates the Cell Loss Priority. The CLP fields are used by the network to decide which cells can be dropped when congestion occurs. A cell with a lower priority is the first candidate for dropping.

The universal transport processing (multiplexing and routing) for B-ISDN is performed by ATM, which enables integrated transport of multirate traffic. ATM cells form the payload portion of the SONET frame in the B-ISDN framework.

Figure 2-4: ATM Cell Format

# 2.3 ATM Delineation

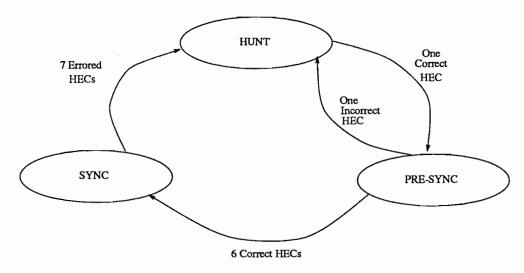

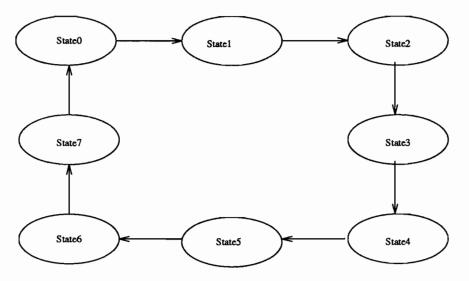

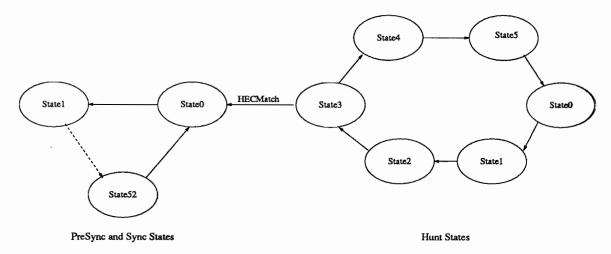

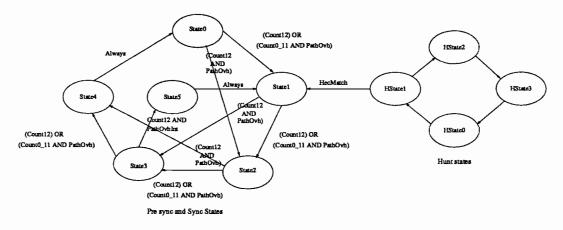

If ATM cells form the payload of the SONET frame, the receiver must synchronize with the incoming byte stream. It will then be able to separate the ATM cells and store them for further processing. This is the primary purpose of the ATM receiver, described in this report. Cell delineation is achieved by using the HEC (Header Error Check) field in the ATM cell header to determine if synchronization has been attained [1]. Figure 2-5 shows the state diagram for receiver cell synchronization.

Figure 2-5: ATM Cell Delineation State Diagram

Initially, the delineation unit checks each input stream, byte by byte to see if the HEC of the first four bytes of the assumed header field matches the fifth byte. If it does, the process passes to pre-sync. In the pre-sync phase, the unit checks for valid headers after every 53 bytes. If HEC matches six consecutive times, the unit assumes that it is synchronized with the received stream. The delineation unit constantly checks to see if the input stream is in sync. If it encounters seven consequent cells for which the HECs do not match, it re-initializes itself and begins to hunt for synchronization once again.

#### 2.4 The AN2 ATM Switch

The AN2 LAN is a switch based local area network [2]. Hosts are connected to switches by one or more 155 Mb/s full duplex links, and switches are interconnected by either 155 Mb/s or 622 Mb/s links. Switches are 16 by 16 port crossbars. The AN2 is a virtual circuit based system. The AN2 switches guarantee ordered delivery of cells within a virtual circuit. There is no head of line blocking in the switch. The switches implement a hop-by-hop based flow control scheme. The following two types of line cards plug into switch crossbar:

- 1. host line cards have four full duplex links operating at 155 Mb/s, and

- the AN2/SONET Gateway operating at 622 Mb/s using the SONET transmission protocol.

The input side of the line card receives cells over the link, routes those cells, queues them, and sends them through the crossbar. The output side receives cells from the crossbar, buffers them, transmits the cells on the link and manages the flow control mechanism. Queues will never overflow because of the flow control mechanism.

Cells are synchronously switched through the crossbar with a slot period of 520 ns. During arbitration, lasting one slot period, each line card requests access to each output line card for which it has traffic. The arbitration mechanism will result in either no connection or a single connection to an output line card. Cells from the crossbar are immediately transmitted on the output link.

The AN2 implements a strict, window flow control mechanism on a link by link and virtual circuit by virtual circuit basis. During call setup, buffers are allocated on the input side of each line card along the route for the virtual circuit. A line card will not transmit a cell on a link unless it is sure there is a buffer at the receiving end to store that cell. The line card outputs maintain an account balance of the number of buffers available at the receiver for each virtual circuit, which is decremented as each cell is transmitted. When the account balance reaches zero, the output notifies the input line card, through the crossbar, to stop the virtual circuit.

The output side of a line card piggybacks the virtual circuit identifier of a forwarded cell on the cell stream going back to the far end. This serves as an acknowledgement that will be used by the output side of the far end line card to increment its account balance for that virtual circuit.

Each line card has a microprocessor, called the LCP, to monitor, control, and manage the line card. The LCP is involved in call setup, call tear down, route

finding, resource allocation, periodic bandwidth allocation, monitoring the line card and performance measurement.

# 2.5 The Gateway Card

The AN2/SONET Gateway is a hardware device that connects the Digital Equipment Corporation AN2 Local ATM network to the SONET based B-ISDN ATM network [2]. The purpose of the gateway is to provide a means for data to move between the AN2 and the SONET based wide area network.

The AN2/SONET Gateway is a single card that plugs into an AN2 switch port. The AN2/SONET Gateway supports the following features:

- operation at the SONET STS-12/STS-12c(622.08 Mb/s) capacity on the wide area side via fiber optic connection

- operation within the DEC AN2 Local ATM switch by connecting to the AN2 switch backplane

- experimental techniques for dynamic bandwidth allocation

- experimental techniques for interoperability between connection-oriented and connection less protocols

- experimental signaling protocols for call setup and call parameter negotiations

- measurement of network performance

#### 2.5.1 Transmit Section

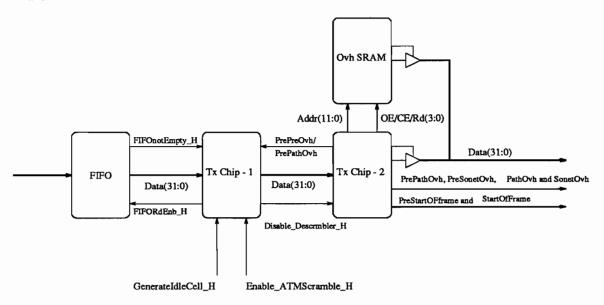

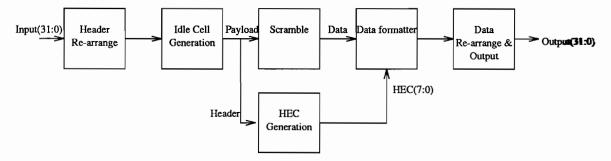

The transmit section, connects the AN2 switch crossbar to the transmit SONET Network Termination Equipment (NTE) of the WAN provider. The transmit section will normally use clocks derived from the receive section, but will also have a crystal controlled local clock oscillator. The transmitter receives ATM cells from the AN2 crossbar. The cells are buffered and merged with the SONET overhead information stream. The combined stream forms a SONET frame. The transmit section will maintain status information including the number of buffers available at the remote for each possible virtual circuit. The transmit section supports a single STS-12c stream or four STS-3c streams multiplexed into a single STS-12. A block diagram of this section is given in Figure 2-6.

Figure 2-6: Block diagram of the transmit section of AN2/SONET Gateway Card.

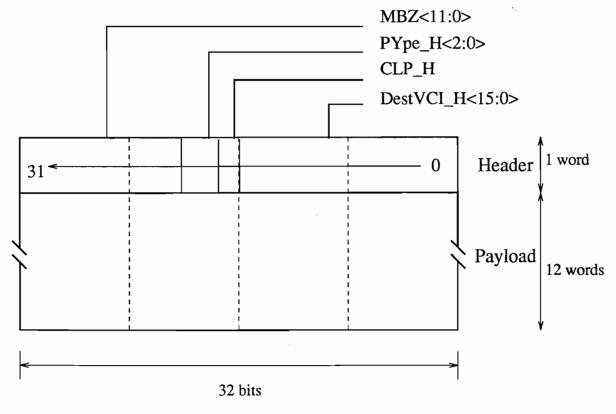

ATM cells are written into the transmit FIFO by the AN2 switch. Cells are received at the FIFO in thirteen clock cycles, 32 bits per cycle. The transmit section only accepts cells destined for the gateway.

A complete cell is written into the FIFO on successful arbitration, if there are sufficient buffer resources in the FIFO.

The FIFO is used to temporarily buffer cells arriving from the crossbar. It also serves as a rate adaptation unit. The AN2 operates at a clock rate of 40 ns (25 MHz) per 32 bit word and a cell rate of 520 ns, since 13 words per cell are forwarded across the AN2 crossbar (the HEC byte is not passed through the crossbar). In contrast, the SONET transmission clock is 12.86 ns per byte or 681.6 ns per cell. Cells are written into the FIFO at AN2 rate and read out at the SONET rate. The switch arbitration mechanism insures the FIFOs do not overflow.

The SONET Transpose and ATM Scramble unit operates in one of two modes: a single STS-12c ATM stream, or four STS-3c ATM streams multiplexed into an STS-12. The mode is selected at system configuration time. The functionality and design of this unit is described in the next chapter, *Transmitter Design*.

The SONET overhead RAM is a fast, dual-ported SRAM containing the SONET overhead bytes. The LCP loads the SONET overhead RAM with the proper section, line and path overhead bytes. Sixteen overhead buffers are provided so that the contents can be altered while the system is in operation. The SONET overhead is multiplexed with the byte interleaved ATM cell streams via a tristate bus to generate the input stream to the SONET Formatter.

The SONET Formatter takes payload and overhead data from the preceding stages and performs the combinational operations necessary to fill the parity bytes of the path, section and line overhead, and scrambles the SONET signal according to the standard polynomial [22]. The parallel-serial unit converts the byte-wide parallel stream to a serial stream, which is then fed into the Electrical-to-Optical interface.

The transmit section is implemented using a combination of Xilinx FPGAs, a commercially available SONET parallel to serial conversion integrated circuit,

and commercially available memory chips.

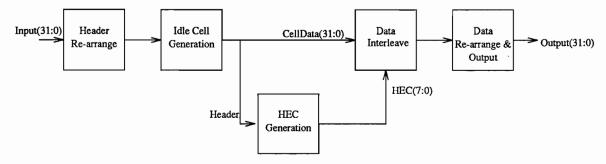

#### 2.5.2 Receive Section

The receive section, shown in Figure 2-7, connects to the received signal from the wide area SONET NTE. Timing information (bit, byte and frame) is extracted from the received SONET signal, and is used in both the receive and transmit sections. The receive section extracts the SONET overhead and the SONET payload from the incoming stream. The SONET payload is processed as ATM cells in accordance with evolving SONET/ATM standards. The ATM header is checked for errors prior to further processing. ATM cells are buffered on a virtual circuit basis. The destination of the received ATM cells is determined by a routing table. The receive section supports a single STS-12c stream or four STS-3c streams multiplexed into a single STS-12.

Figure 2-7: Block diagram of the receiver part of AN2/SONET Gateway Card.

The Optical-to-Electrical converter receives and detects the optical serial bit stream and outputs an electrical serial bit stream. A bit clock is recovered from the received signal. The SONET Synchronization and Serial-Parallel unit searches for and synchronizes itself with the SONET frame synchronization pattern. The byte clock generated by this unit is used throughout the gateway system. The SONET Synchronization and Serial-Parallel unit converts the serial bit stream to a 32-bit wide parallel stream for further processing.

The SONET Descramble and BIP check unit applies the standard descrambling function to the received signal [22]. This unit also checks the SONET section and line bit interleaved parity (BIP) bytes.

The ATM Cell Delineation and Descramble unit searches for valid ATM cell headers in the received payload byte stream, using the standard cell synchronization method. The design of this part is described in the chapter Receiver Design.

After the cells are delineated and descrambled, partial cells are written to the SRAM unit for buffering and routing. The SRAM unit also provides the rate adaptation between the SONET and AN2 crossbar clock rates. The SRAM unit performs buffering of the ATM cell streams prior to buffering on a per VCI basis in the VRAM unit. The SRAM unit is managed by the Cell Stream Management unit, which schedules memory accesses for the cell streams and provides indication when cells are ready to be buffered in the VRAM. The Cell stream management unit also controls VC extraction from the received cells.

The VRAM buffer is used to provide sufficient buffering for ATM cells, so that congestion in the AN2 network will not cause cell loss due to buffer overflow. The cells are buffered on a per VCI basis, so that flow control on one VC will not effect other VCs.

The receive section is implemented using a combination of Xilinx FPGAs, a commercially available SONET synchronizer integrated circuit, a three port video dynamic access memories for the VRAM Buffer, and commercially available memory chips.

#### 2.5.3 The Line Card Processor

The Line Card Processor (LCP) manages the resources of the receive section, transmit section, and communications paths [2]. It is responsible for setting up circuits, releasing circuits, monitoring circuits, allocating bandwidth to circuits, and other network management operations both within the AN2 and with the WAN. The LCP communicates with other switch processors via ATM cells. The LCP is composed of a general purpose RISC processor and support chips.

### 2.6 Xilinx FPGAs

The Xilinx field programmable gate array is a regular array of configurable logic blocks (CLBs) with programmable routing resources. The designs presented here use two different types of Xilinx chips, the Xilinx XC3190, which has 16 columns and 20 rows of CLBs and the Xilinx XC3195, which has 22 columns and 22 rows of CLBs. These chips may be programmed in place by downloading the appropriate program to the device.

# Chapter 3

# Transmitter Architecture

The transmitter chips form SONET frames from ATM cells and SONET overhead. The transmitter is implemented using one Xilinx XC3195 and one Xilinx XC3190 chip. A block diagram of the transmitter is shown in Figure 3-1.

The first transmitter chip reads its input from the AN2 FIFOs. The input to the second transmitter chip is the data that has been partially processed by the first transmitter. The output of the second transmitter chip is formed of ATM cells arranged contiguously in the payload portion of the SONET frame. A complete SONET frame is formed at the output by multiplexing the payload portion of the SONET frame with the SONET overhead from the overhead SRAMs as shown in Figure 3-1.

The first transmitter chip generates control signals for reading the FIFO. It gets signals from the FIFO indicating whether there are no words in it. Control signals from the second transmitter chip to the first transmitter chip indicate the presence of overhead in the output stream. The signal GenerateIdleCell\_H indicates that the chip should generate idle cells and Enable\_ATMScramble\_H means that the chip should apply the ATM payload self synchronous scrambler to each cell. Enable\_ATMScramble\_H is to be used for diagnostic purposes. The first chip uses two clocks, Xmit\_ByteClk\_H, a 12.86 ns clock and Xmit\_WordClkP0\_H,

#### a 51.44 ns clock.

Figure 3-1: System block diagram of the Transmitter.

Figure 3-2: Data arrangement in the Transmit FIFOs.

The overhead is read out of the overhead SRAMs by enabling them at the appropriate time. The second transmitter chip also generates signals that indicate the start of frame and SONET overhead in the output data stream. The address for the overhead SRAMs are generated by this chip. This chip uses the Xmit\_WordClkP0\_H clock, the 51.44ns clock.

Behavioral models, simulation results and FPGA layouts of the transmitter chips are given in Appendix A for the STS-12c mode and in Appendix B for the 4 x STS-3c mode. The receiver and the transmitter were connected together and simulated. These results are given in Appendix C for the STS-12c mode and in Appendix D for the 4 x STS-3c mode.

# 3.1 Functionality specifications

The functions of the transmitter are summerized below:

- Byte-multiplex ATM cells from a single STS-12c or four STS-3c streams into a single word stream for encapsulation in a SONET frame.

- Insert idle cells into the output data stream when there are no cells available for transmission.

- Calculate and insert the HEC byte into each cell.

- Apply the ATM self-synchronous scrambler operation to each ATM cell payload.

- Generate addresses for the SONET transmit overhead SRAMs.

- Generate control signals to control reading and writing the transmit FIFOs.

#### 3.2 Architecture for the STS-12c mode

### 3.2.1 Datapath of Transmitter Chip1

This chip reads the 32 bit input data from the FIFO. Four 32 bit FIFOs are present on the board. Each ATM cell is arranged in thirteen words within the FIFO, as shown in Figure 3-2. The bit arrangement of the four byte ATM header in the FIFO is also shown in this figure. Cells are read out of the four FIFOs in a round-robin fashion.

The input is read using a 51.44 ns clock, that is generated within the chip using the Xmit\_ByteClk\_H. The input is not read continuously. Normally, the input is read at 51.44 ns intervals, using the internally generated clock. The 51.44 ns clock is delayed by 12.86 ns when the HEC byte or the path overhead is inserted. Thus, when either the HEC or the path overhead byte is inserted, the input is read after 64.3 ns. This clock is used for various operations within the chip. It will be referred to as WdClkShft from now on.

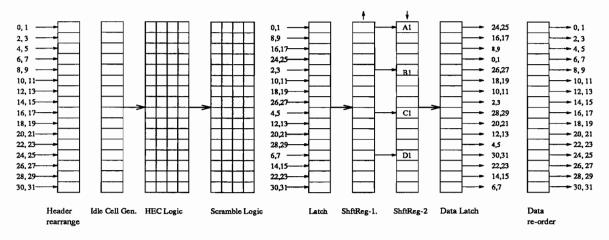

Figure 3-3: Diagram showing the data flow for Chip1 of STS-12c transmitter.

A functional block diagram of the first transmitter chip which shows the data flow through the first transmitter chip is given in Figure 3-3. The data is read from the FIFO and latched at the input IOBs. Then, the header is re-arranged to conform to the first four bytes of a standard ATM cell. Next, an idle cell header is generated. It may be used if actual data is unavailable for transmission. Next, the HEC is calculated over the first four bytes of the header word.

Figure 3-4: Datapath organization for STS-12c transmitter - Chip1.

The next operation is the ATM self synchronous scrambling. The payload portion of the ATM cell is scrambled before transmission. The data is then reordered and latched. Finally, the data is formatted to insert the header into the ATM cell and arrange the ATM cells contiguously.

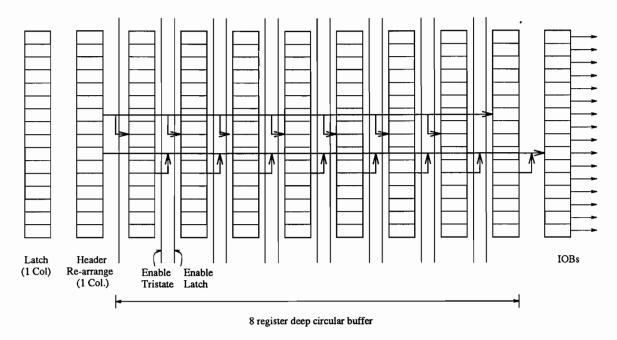

The Xilinx floor plan for the STS-12c mode is as shown in Figure 3-4. The first column in the figure is used for *Header re-ordering*. The order of the bits in the input header word is shown in Figure 3-2. The bits are re-arranged to confirm to the standard ATM cell header [1]. Thus, this column performs a multiplexing operation. When the input data is the header word, it re-arranges the word to form a standard ATM header. When the input is payload data, it just latches the data. The header rearrange column operates using the WdClkShft clock.

The next column is used for *Idle Cell Generation*. Idle cells are required to have the header bit pattern shown in Figure 3-5. This column implements a multiplexer. The output of this column is either the first four bytes of the idle cell header or the input data. The idle cell generation column uses the WdClkShft clock.

The next three columns are used for HEC calculation. HEC is calculated on ATM cell headers including idle cell headers. A signal from the state machine enables HEC calculation when the header is at the input of the HEC calculation

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | . 0 |

|---|---|---|---|---|---|---|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0 | 0 | 0 | 0 | a | a | a | 0   |

"a" indicates that the bit is available for the appropriate ATM layer function.

Figure 3-5: Header bit pattern for an idle cell

logic. The HEC calculation is done using the WdClkShft clock.

The polynomial used to calculate the HEC is given below:

$$1 + x + x^2 + x^8 \tag{3.1}$$

After calculating the HEC, the result is added modulo-2 with the following coset polynomial:

$$1 + x^2 + x^4 + x^6 \tag{3.2}$$

Thirty two bit parallel HEC calculating circuit is implemented in these designs. The equations used for this purpose are given below. In these equations, c is the coset polynomial, h is the input 32 bit word on which the HEC is to be calculated and r is the resultant HEC vector. In the input 32 bit header,  $h_0$  is the most significant bit and  $h_{31}$  is the least significant bit.

$$c := "01010101";$$

$$r_0 := h_0 + h_1 + h_3 + h_8 + h_{10} + h_{12} + h_{13} + h_{15} + h_{17} + h_{19} + h_{23} + h_{24} + h_{25} + h_{31};$$

$$r_1 := h_1 + h_2 + h_3 + h_7 + h_8 + h_9 + h_{10}$$

$+h_{11} + h_{13} + h_{14} + h_{15} + h_{16} + h_{17}$

$+h_{18} + h_{19} + h_{22} + h_{25} + h_{30} + h_{31};$

$$r_2 := h_2 + h_3 + h_6 + h_7 + h_9 + h_{14} + h_{16}$$

$$+ h_{18} + h_{19} + h_{21} + h_{23} + h_{25} + h_{29}$$

$$+ h_{30} + h_{31};$$

$$r_3 := h_1 + h_2 + h_5 + h_6 + h_8 + h_{13} + h_{15} + h_{17} + h_{18} + h_{20} + h_{22} + h_{24} + h_{28} + h_{29} + h_{30};$$

$$r_4 := h_0 + h_1 + h_4 + h_5 + h_7 + h_{12}$$

$+ h_{14} + h_{16} + h_{17} + h_{19} + h_{21} + h_{23}$

$+ h_{27} + h_{28} + h_{29};$

$$r_5 := h_0 + h_3 + h_4 + h_6 + h_{11} + h_{13} + h_{15} + h_{16} + h_{18} + h_{20} + h_{22} + h_{26} + h_{27} + h_{28};$$

$$r_6 := h_2 + h_3 + h_5 + h_{10} + h_{12} + h_{14} + h_{15} + h_{17} + h_{19} + h_{21} + h_{25} + h_{26} + h_{27};$$

$$r_7 := h_1 + h_2 + h_4 + h_9 + h_{11} + h_{13} + h_{14} + h_{16} + h_{18} + h_{20} + h_{24} + h_{25} + h_{26};$$

r := r + c;

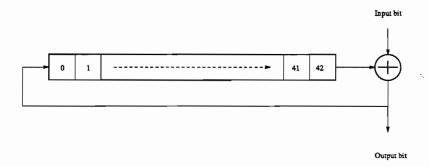

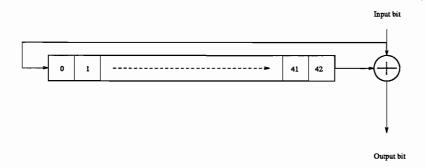

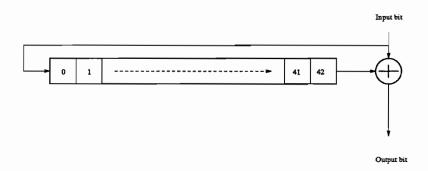

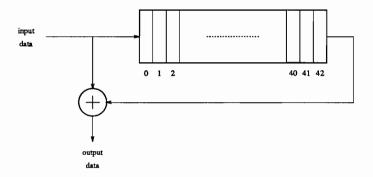

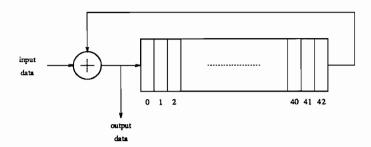

The ATM self synchronous scrambler is implemented in the next three columns. Only the payload portion of an ATM cell is scrambled. The scrambler uses the WdClkShft clock. Scrambling is performed using the following polynomial [3]:

$$x^{43} + 1$$

(3.3)

A conceptual diagram illustrating the operation of the scrambler is shown in Figure 3-6.

Figure 3-6: Conceptual diagram of the scrambler.

The scrambler used in this design is a 32 bit parallel scrambler. The equations used to implement the 32 bit parallel scrambler are given below.

```

FOR I IN 0 TO 31 LOOP

Scrambled_Data(I) <= Input_Data(I) XOR Scramble_State(42-I);

END LOOP;

FOR I IN 0 TO 31 LOOP

Scramble_State(31-I) <= Input_Data(I) XOR Scramble_State(42-I);

END LOOP;

FOR I IN 32 TO 42 LOOP

Scramble_State(I) <= Scramble_State(I-32);</pre>

```

#### END LOOP;

The next column is used to latch the data out of the scrambler. The data is re-arranged before latching into this column. The order of the input bits to this column is shown in Figure 3-4. The *Latch* column uses WdClkShft clock.

The input to the Latch register is re-arranged as shown in Figure 3-4 to localize the interconnections in ShiftReg-1 and ShiftReg-2. The output of Latch is latched and operated upon by ShiftReg-1 and ShiftReg-2. Both of these registers operate using the Xmit\_ByteClk\_H, which is the 12.86 ns clock.

ShiftReg-1 shifts the data up by two bits, that is one CLB every 12.86 ns. ShiftReg-2 shifts the data down two bits every 12.86 ns. With reference to Figure 3-4, ShiftReg-2 gets one byte at CLBs in location A1, B1, C1 and D1 from ShiftReg-1 after each upshift. Using this design, HEC byte or the path overhead byte can be inserted in the output data stream easily.

The HEC byte is inserted by latching the HEC byte at locations A1, B1, C1 and D1 of Figure 3-4, instead of the data from *ShftReg-1*. When the HEC byte is inserted, the data in *ShftReg-1* is not shifted up. This is done by disabling the clock to the *ShftReg-1* column using the enable clock input in the CLBs. As mentioned earlier, the clock period of WdClkShft is 64.3 ns when the HEC byte is inserted. The clock period of WdClkShft is 51.44 ns normally.

The path overhead byte is externally multiplexed at the output of the second transmitter chip. A byte is left empty in the output stream of this chip to insert the path overhead. To leave an empty byte, *ShftReg-1* is not shifted up for one 12.86 clock period. The clock period of WdClkShft is 64.3 ns when the path overhead byte is inserted.

Before the data is read out, it is re-ordered to the normal data order as shown in Figure 3-4. The output is read out using the Xmit\_WordClkP0\_H.

All the ATM processing required for the SONET STS-12c architecture is thus

### 3.2.2 State machine for STS-12c Chip1

The functions performed by the state machine are listed below.

- Generation of the shifted 51.44 ns clock, WdClkShft, a clock that is shifted by 12.86 ns every time the HEC or path overhead is inserted. This clock is masked when SONET overhead is inserted in the output stream.

- A modulo-13 counter using WdClkShft clock. The states of this state machine are shown in Table 3.1. The counter states are used for the following signals:

- A signal to disable scrambling the header word.

- A signal to insert the HEC byte into the data stream.

- A signal to enable header rearrangement.

- A signal to leave a byte empty to insert the path overhead byte when the

word is read out of the second transmitter chip. This signal is generated

using the PrePathOvh signal that is asserted by the second transmitter chip.

- A signal to disable output when SONET overhead is to be multiplexed in the output data stream. This signal is generated using the PrePreOvh signal generated by the second transmitter chip.

Table 3.1 gives the pipeline delay through the chip and the relative timings of the various control signals. Table 3.2 shows the use of the *PrePathOvh* signal to leave a free byte for inserting path overhead. The time ticks in the following tables is not synchronous. Thus, T0 does not refer to the same time tick in all the tables.

| Time tick | Action                                                  |

|-----------|---------------------------------------------------------|

| T0        | Idle cell header generated and is at the output of the  |

|           | idle cell column.                                       |

|           | Disable scrambler signal.                               |

| T1        | Header latched out of the scrambler without scrambling. |

|           | HEC calculation logic stage 1 enable.                   |

| T2-t0     | HEC calculation logic stage 2 enable.                   |

|           | Data is at the output of Latch column.                  |

|           | Parallel loading of ShftReg-1 register is enabled.      |

| T2-t1     | Data latched out of ShftReg-1 column.                   |

| T2-t2     | First byte out of the ShftReg-2 column.                 |

| T2-t3     | Second byte out of ShftReg-2 column.                    |

| T3-t0     | Third byte out of ShftReg-2 column.                     |

| T3-t1     | Fourth byte out of ShftReg-2 column.                    |

|           | HEC selection is enabled.                               |

|           | 51.44 ns clock shifted for a 12.86 ns.                  |

|           | Clock to ShftReg-1 is disabled.                         |

| T12       | Idle cell generation is enabled if no cells are         |

|           | available for transmission or if external               |

|           | GenerateIdleCell_H signal is asserted.                  |

Table 3.1: Pipeline delay through Chip1 illustrating the generation of control signals.

| Time tick | Action                                                 |

|-----------|--------------------------------------------------------|

| T0-t0     | PrePathOvh signal latched into first transmitter chip. |

| T0-t1     | PrePathOvh signal width reduced to 12.86 ns.           |

| T0-t2     | PrePathOvh signal delayed by 12.86 ns.                 |

| T0-t3     | PrePathOvh signal used to disable clock to ShftReg-1.  |

| T1-t0     | 1 byte is left empty for path overhead insertion.      |

Table 3.2: Relative timing of PrePathOvh signal to the actual path overhead byte.

| Time tick  | Action                                                       |

|------------|--------------------------------------------------------------|

| T0         | PrePathOvh signal generated.                                 |

| T1         | PrePathOvh signal latched out of second chip.                |

| T2         | PrePathOvh signal latched into first chip.                   |

| Т3         | First byte of the word left empty for path overhead.         |

| T4         | Word with the path overhead byte out of DataLatch register   |

|            | in Figure 3-4.                                               |

| T5         | Word with path overhead byte out of first transmitter chip.  |

| T6         | Word with path overhead byte into second transmitter chip.   |

|            | PrePreOvh signal latched out of second transmitter chip.     |

| <b>T</b> 7 | Read/output enable of overhead SRAM latched out of chip.     |

|            | First SONET overhead word read into the output stream.       |

| T8-T15     | SONET overhead words read into the output stream.            |

| T16        | Word with path overhead read out of the transmitter.         |

|            | Only LSB of overhead SRAM enabled to merge the path overhead |

|            | byte into the output stream.                                 |

| T17-T269   | Payload of SONET framed is read out of the transmitter.      |

Table 3.3: Second transmitter chip control signals.

### 3.2.3 Transmitter Chip2 design for the STS-12c mode

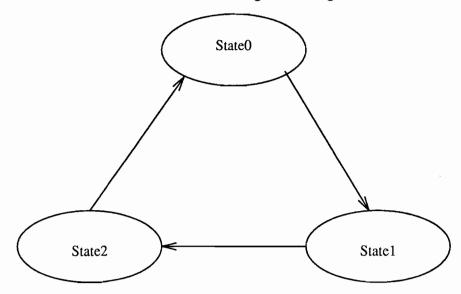

The second transmitter chip generates the SONET overhead SRAM addresses. It generates signals to indicate SONET overhead and path overhead in the output data stream. It generates a signal to indicate the beginning of a new SONET frame. These signals are used by the SONET BIP scrambler chip. The signals PrePreOvh and PrePathOvh are used by the first transpose chip. The output of this chip consists of complete SONET frames in which the ATM cells are arranged contiguously. Table 3.3 shows the SONET overhead counter states and the pipeline delay through the transmitter.

# 3.3 Design for the 4 x STS-3c mode

#### 3.3.1 Data path design for the first transmitter chip

This chip reads the 32 bit input data from the FIFO. Four 32 bit FIFOs are present on the board. Each ATM cell is arranged in thirteen words within a FIFO, as shown in Figure 3-2. The bit arrangement of the four byte ATM header in the FIFO is also shown in this figure. The FIFOs are written by the AN2 crossbar. Each FIFO consists of data for a single channel. For broadcast or multicast, all the FIFOs will be simultaneously written with the same data by the AN2 crossbar. The chip reads the FIFOs in a round-robin fashion. Thus, during each clock cycle, a word from a single channel is read by the chip.

Figure 3-7: Data path of first transmitter chip

A functional block diagram illustrating the data flow through the first transmitter chip is shown in Figure 3-7. Two clocks are used within the chip. A 51.44 ns clock and a 12.86 ns clock. The 51.44 ns clock will be referred to as WdClkShft and the 12.86ns clock will be referred to as ByteClk. The WdClkShft is generated within the chip and will be masked when the SONET overhead or the path overhead is inserted.

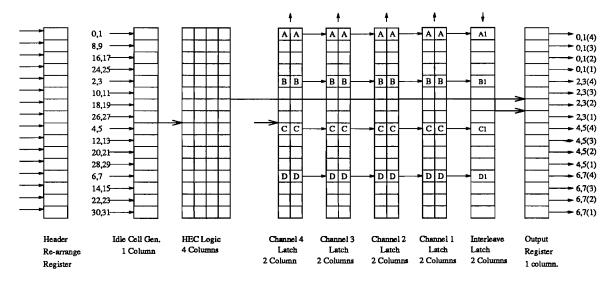

The Xilinx floor plan for this chip is as shown in Figure 3-8.

The input data is latched in the input IOBs. Then, the header is re-arranged in the first column. The header re-arrange column is same as the STS-12c mode.

The next column is used for idle cell generation. This column implements a

Figure 3-8: Data path of first transmitter chip

multiplexer. The output of this column is either the first four bytes of the idle cell header or the input data. The data out of this column is as shown in Figure 3-8. The idle cell generation column uses the WdClkShft.

The next four columns are used to generate the HEC. The HEC polynomial is the same as the one used for the STS-12c mode. The 32 bit parallel HEC implementation that was used in the STS-12 mode is also used here.

The headers of the four channels are read sequentially. The HECs of all the four channels are calculated one after the other and stored in the next column. The HEC bytes of the four channels are stored in this column in a byte interleaved fashion. Thus, this interleaved word can be directly multiplexed at the output, when required.

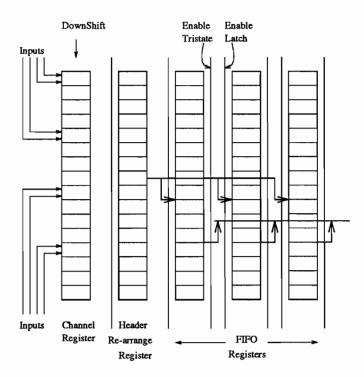

The Channel registers are used to byte interleave the data. The CLBs A, B, C and D in Figure 3-8 function using the ByteClk. The other CLBs of the Channel registers function using the WdClkShft. Two columns are used for each channel. While one column is used to buffer the data, the data in the other column is used to form the interleaved word which is output. Byte interleaving is explained below.

Interleaving is achieved by getting a byte from the Channel 1 register into locations A1, B1, C1 and D1 of the Interleave Latch once every ByteClk. The data in this register is down shifted using the ByteClk. The data is also right shifted from the Channel 4 register to Channel 3 to Channel 2 to the Channel 1 register using the ByteClk. After four ByteClk periods, which is 51.44 ns, the interleave register contains one complete byte interleaved word.

The Channel registers are shifted up using the WdClkShft. By repeating this operation, all the data in one set of the four channel registers are used to form interleaved words at the end of four WdClkShft periods. In the mean time, four new words have been written into the other set of four Channel registers.

A new word is written into one of the two Channel-4 registers at every WdClk-Shft. One set of the Channel-4, Channel-3, Channel-2 and Channel-1 registers are connected in a shift register configuration to read the input data. The input data is right shifted from Channel-4 to Channel-3 to Channel-2 to Channel-1 register. Thus, after four clock periods, four new words have been written into the channel registers. For the next four WdClkShft periods, these words will be used to form the interleaved words. The other set of four channel registers that were used to form the output words will be used during the next four clock periods to buffer the input.

The output of the interleave register is read in by the output register. This register also multiplexes the HEC word and the data word from the interleave register. When HEC word is to be inserted, the Sel\_Hec control signal goes high and the HEC is selected instead of the data word from the interleave register. At the same time, the clocks to the interleave register and the channel registers are disabled. Clocks to all the registers using ByteClk are disabled by using the enable clock input in a CLB. The WdClkShft is masked when HEC is inserted.

During SONET overhead or path overhead insertion, all the CLBs within the chip are disabled and the input is also disabled. The ByteClk as well as the WdClkShft are masked to disable the operations within the chip.

#### 3.3.2 State machine for the 4 x STS-3c Chip1

The various signals generated by the state machine and their significance is given below:

- WdClkShft: This clock is the same as the Recv\_WordClkP0\_H, except that

it is masked for one clock cycle when the HEC byte is inserted. It is also

masked for the time when the path overhead or the SONET overhead is

inserted.

- A six bit counter that counts from 0-51 using WdClkShft. It only counts 52 states because WdClkShft is masked for the state when HEC is inserted. This counter is used to generate the following control signals:

- Header rearrange control: To re-arrange the header word.

- Idle cell generation: Idle cells need to be generated when either the GenerateIdleCells input signal is high or when there are no cells in the FIFOs. Idle cells will be generated only after the transmission of the present cell.

- HEC generation controls: The HEC logic is enabled appropriately to latch the headers and generate HECs.

- Enable clock to the channel registers: CLBs A, B, C and D in Figure 3-8 will be disabled whenever the HEC is inserted. The clock that is used by these CLBs is already masked when path overhead or SONET overhead is to be inserted. This signal also controls the enable to these CLBs when the CLBs are used to buffer the words. These CLBs operate

at the 12.86 ns clock only when they are used to form the interleaved word.

- Parallel load/ right shift control: For the set of channel registers that are used to interleave the data, the CLBs A, B, C and D will get the data from the CLBs directly below them once every four 12.86 ns clock periods. During other times, these CLBs will right shift the data. For the set of channel registers that are used to buffer data, all the CLBs are parallelly loaded every 51.44 ns.

- Select HEC control: This is used to multiplex the data input to Output register.

- PrePreOverhead and PrePathOverhead signals are used to mask the generation of WdClkShft and ByteClk.

The relative timing of the control signals and the pipeline delays for a single channel are illustrated in Table 3.5. The clock period  $T_x$  represents a 51.44 ns clock, that is synchronous to Xmit\_WordClkP0\_H and  $t_x$  represents the 12.86 ns clock period.

### 3.3.3 Design of the second transmitter chip for 4 x STS-3c mode

This chip scrambles the byte interleaved data that it receives from the first chip. An 8 bit self synchronous scrambler is implemented in this design. The scrambler occupies the first seven columns of CLBs in the chip. Equations for the scrambler are given next in VHDL:

| Time tick | Action                                                               |

|-----------|----------------------------------------------------------------------|

| T0        | Generate signal HeaderCtl to re-arrange header bits                  |

|           | to form Stream-1 header.                                             |

|           | Enable FIFO to read the Stream-1 header word.                        |

| T1        | Stream-1 header at the input of Header Rearrange column.             |

| _         | HeaderCtl signal at the input of Header Rearrange                    |

|           | column.                                                              |

| <b>T2</b> | GenerateIdleCell signal latched out if there are no cells            |

|           | in stream-1 available for transmission or if the input               |

|           | GenerateIdleCell_H is asserted.                                      |

|           | Header for stream-1 is at the input of idle cell column.             |

| T3        | Stream-1 header is at the input of Channel 4 latch.                  |

|           | Stream-1 header is at the input of stage 1 of HEC calculation logic. |

|           | Clock to first stage of HEC calculation logic is enabled.            |

| T4        | Stream-1 header is at the input of Channel 3 latch.                  |

|           | Stream-1 header is at the input of stage 2 of HEC calculation logic. |

|           | Clock to second stage of HEC calculation logic is enabled.           |

| T5        | Stream-1 header is at the input of Channel 2 latch.                  |

|           | HEC for stream-1 is calculated and is ready to be latched into       |

|           | the HEC interleave register.                                         |

|           | Clock to HEC interleave register enabled.                            |

| T6        | Stream-1 header is at the input of Channel 1 latch.                  |

| T7-t0     | Stream-1 header is at the output of Channel 1 latch, i.e at          |

|           | the input of interleave latch.                                       |

| T7-t1     | First header byte latched out of interleave latch.                   |

| T7-t2     | First byte of stream-2 header latched out of interleave latch.       |

| T7-t3     | First byte of stream-3 header latched out of interleave latch.       |

| T8-t0     | First interleaved header word latched out of interleave latch.       |

| T8-t1     | The interleaved header word is latched out of output register.       |

Table 3.4: Pipeline delay through Chip1 illustrating the generation of control signals for the 4 x STS-3c mode.

| Time tick | Action                                                            |

|-----------|-------------------------------------------------------------------|

| T9-t0     | The interleaved header word is latched out of Chip1 using         |

|           | Xmit_WordClkP0_H.                                                 |

| T9-t1     | Second interleaved header word is latched out of output register. |

| T10-t0    | The second interleaved header word is latched out of Chip1.       |

| T10-t1    | Third interleaved header word latched out of output register.     |

| T11-t0    | Third interleaved header word latched out of Chip1.               |

|           | Generate signal to mask clock to all the logic within the first   |

|           | chip other than the output, which uses Xmit_WordClkP0_H.          |

| T11-t1    | Fourth interleaved header word latched out of output register.    |

| T12-t0    | Fourth interleaved header word latched out of Chip1.              |

|           | Interleaved HEC word latched out of output register.              |

Table 3.5: Pipeline delay through Chip1 illustrating the generation of control signals for the 4 x STS-3c mode.

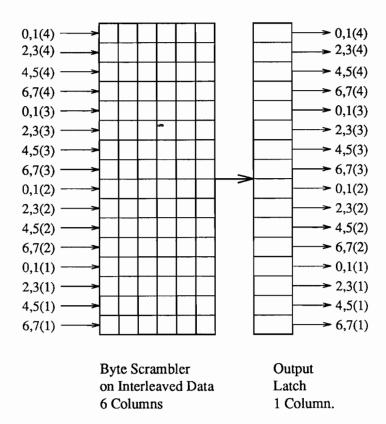

Only the ATM cell payload is scrambled. Scrambling is controlled by the Enable\_Scrambler signal from the first transmitter chip that goes low to disable scrambling. This signal will go low when the header is at the input of the scrambler or when the external control disables scrambling by asserting the external signal Enable\_ATMScramble\_H to low. The organization of the data path for this chip is shown in Figure 3-9.

Chip2 generates the SONET overhead SRAM addresses. It generates signals to indicate SONET overhead and path overhead in the output data stream. It also generates a signal to indicate the beginning of a new SONET frame. These

Figure 3-9: Data path of first transmitter chip

| Time tick | Action                                                       |

|-----------|--------------------------------------------------------------|

| T0        | PrePathOvh signal generated.                                 |

| T1        | PrePathOvh signal latched out of second chip.                |

| T2        | PrePathOvh signal latched into first chip.                   |

| Т3        | All the clocks in first chip other than Xmit_WordClkP0_H are |

|           | disabled.                                                    |

| <b>T4</b> | Path overhead word is latched out of output latch            |

|           | in Figure 3-8.                                               |

|           | PrePreOvh signal latched out of Chip2.                       |

| T5        | Path overhead word latched out of Chip1.                     |

|           | PrePreOvh signal latched into Chip1.                         |

| T6        | Path overhead word ready to be latched out of Chip2 IOBs.    |

|           | PrePreOvh signal used to generate disable all functions in   |

|           | Chip1.                                                       |

| T7        | Read/output enable of overhead SRAM latched out of Chip2.    |

|           | First SONET overhead word read into the output stream.       |

| T8-T15    | SONET overhead words read into the output stream.            |

| T16       | Path overhead word read into the output stream.              |

| T17-T269  | Payload of SONET framed is read out of the transmitter.      |

Table 3.6: Second transmitter chip control signals.

signals are used by the SONET BIP scrambler chip. The signals PrePreOvh and PrePathOvh are used by the first transmitter chip. The scrambler is also disabled when SONET overhead is multiplexed in the output data stream. The output of this chip consists of complete SONET frames in which the ATM cells are arranged contiguously. SONET overhead is multiplexed externally by enabling the output of the overhead SRAMs at the appropriate time.

Table 3.6 shows the SONET overhead counter states and the pipeline delay through the transmitter.

# 3.4 Design for the STS-12c transmitter using 51.44 ns clock

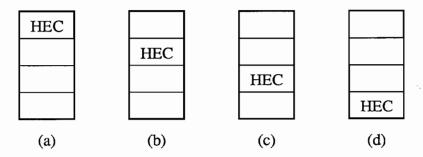

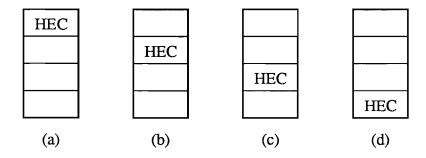

In this section, a way of performing all the transmitter functions using the 51.44 ns clock is presented, keeping the input and output specifications unchanged. In the design that was presented earlier, there are two operations that are performed at 12.86 ns. First, insertion of the HEC byte into the output data stream and next, insertion of the path overhead byte into the output data stream. Due to the odd number of bytes in the ATM cell, the position of the HEC byte in the output data stream could be in one of the four positions shown in Figure 3-10.

Figure 3-10: Position of the HEC byte in the output data stream.

To insert the HEC byte into the output data stream, the input data has to be shifted down by one, two or three bytes depending upon where the HEC byte is to be inserted. The input bytes that are unused for forming the present output word will be used in the next output word. The path overhead is always inserted in bits (7:0) of the first word following the SONET overhead.

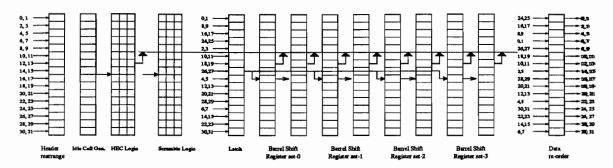

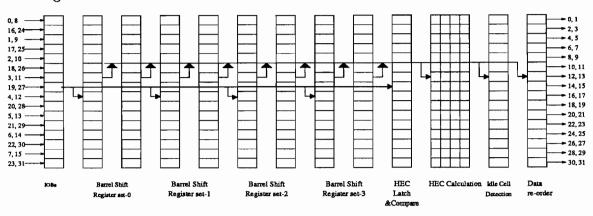

To perform these functions, four sets of barrel shift registers are required. The Xilinx XC3195 floor plan is as shown in Figure 3-11. The first eight columns are used for header rearrange, idle cell generation, HEC logic, and ATM self synchronous scrambling. The data is then re-ordered as shown in Figure 3-11 and latched into the latch column. The re-ordering will reduce the net routing distances. The re-ordered data is latched into the first register of each barrel shift

Figure 3-11: Transmitter design for STS-12c mode using 51.44 ns clock.

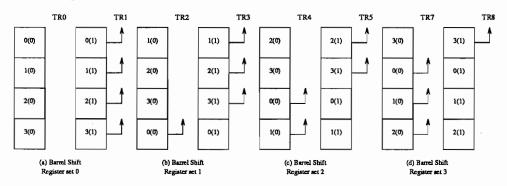

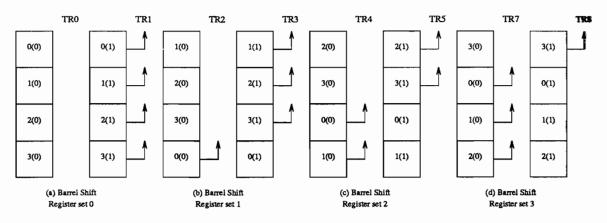

register set. Figure 3-12(a) shows the byte ordering within the first barrel shift register set. Figures 3-12(b), 3-12(c) and 3-12(c) show the byte ordering within barrel shift register sets 1, 2 and 3 respectively. In this figure, bytes 0(0), 1(0), 2(0) and 3(0) correspond to the first register of the register set. Bytes 0(1), 1(1), 2(1) and 3(1) correspond to the second register of each register set. The bytes 0(1), 1(1), 2(1) and 3(1) are delayed by one 51.44 ns clock with respect to bytes 0(0), 1(0), 2(0) and 3(0). Due the order of the bits in the input bus, the maximum vertical net length to realize the byte order shown in Figure 4-24 is 3 CLBs.

The input data is latched into the first register of each barrel shift register sets during each clock period. The data in the first register of each set is latched into the second register at the same time.

Figure 3-12: Byte configurations within the barrel shifter

The output data word is formed by selectively enabling the output tristate enable signals to latch the data onto horizontal long lines.

This process will be clear with an example. If the previous HEC byte was

inserted in the position shown in Figure 3-10(a), then barrel shift register set 1 will be used to form the output for the next cell. The byte configuration for barrel shift register 1 is shown in Figure 3-12(b). To form an output word out of this register, bytes 1, 2, and 3 are latched out of register 1 and byte 0 is latched out of register 0. Note that the word in register 1 was latched one clock cycle before the word in register 0. Hence, the output word ordering is actually bytes 0, 1, 2 and 3, which is the right order.

Output will continue to be generated from barrel shift register set 1 until the next HEC byte or path overhead byte is to be inserted. After inserting the HEC or path overhead, output will be read from barrel shift register set 2. To form an output word out of this register, bytes 2 and 3 are latched out of register 1 and bytes 0 and 1 are latched out of register 0.

Barrel shift register set 2 will be used to form the output if the HEC byte was inserted as in Figure 3-10(b) and barrel shift register set 3 will be used if the HEC byte was inserted as in Figure 3-10(c). If the HEC byte was inserted as in Figure 3-10(d), then barrel shift register set 0 will be used to output the data for the next cell. After inserting four HEC bytes or three HEC bytes and a path overhead byte, one input read operation will be skipped.

The insertion of path overhead byte is similar to the insertion of HEC byte. The path overhead byte will always be inserted in bits (7:0). If the output was being read from barrel shift register set 0 before the path overhead was inserted, after the insertion, the output will be read from barrel shift register set 1. That is, the output will be read from the next set of barrel shift registers after inserting the path overhead.

The state machine for this scheme would have five master states. In the first state, barrel shift register set 1 is used to output the data. In the second state, barrel shift register set 2 is used to form the output and in the third and fourth states, barrel shift register set 3 and barrel shift register set 0 form the output

words, respectively. During the fifth state, the input read operation is skipped. The output of the latch forms the input for all the six barrel shift registers, as shown in Figure 3-11. The outputs of all the barrel shift registers are connected to the horizontal long lines through the tri-state buffers. These tri-state buffers are enabled selectively by the state machine.

# 3.5 Design for 4 x STS-3c transmitter using 51.44 ns clock

In the design that was presented earlier, byte interleaving was the only function that was performed using an 77.76 MHz clock. In the design presented here, all the functions can be performed using a 19.44 MHz clock.

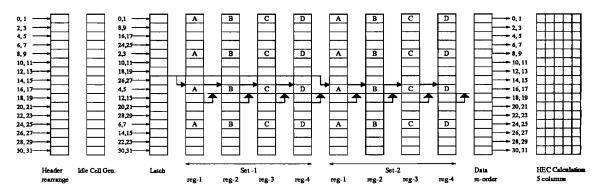

Figure 3-13: Transmitter design for STS-3c mode using 51.44 ns clock.

The floor plan for the design using Xilinx XC3195 is shown in Figure 3-13. After performing header rearrange and idle cell generation functions, the data is re-arranged and latched into the *Latch* column in Figure 3-13. Two sets of registers are used for byte interleaving. The output of *Latch* is latched into either the first register of the first set or the first register of the second set of registers. The two sets of registers are alternated to form the output interleaved word. When one set of registers is used to form the output word, the other set is used to buffer the input words.

To buffer the input words, the four registers within a set can be connected in a shift register configuration, so that the load on the input bus will not be high. The input is latched into register 1 of set 1 or register 1 of set 2. During each clock, the data is shifted right to the next register within a set. Thus, at the end of four clock periods, four new words are present that can be used to generate the output. The word in reg-1 in Figure 3-13 corresponds to the stream 1 input word.

The word in reg-2 corresponds to the stream 2, the word in reg-3 corresponds to stream 3 and the word in reg-4 corresponds to stream 4 input words.

Figure 3-14: CLB output connections to long lines for 4 x STS-3c mode transmitter.

To interleave the bytes at the output the horizontal long lines are used as shown in Figure 3-14. Figure 3-14 shows the top four CLBs of both sets. Assume that the present output word is generated using the data in set 2 registers. With reference to Figure 3-13, only CLBs A, B, C and D of set 2 are used to generate the interleaved word during a given clock period. All the registers of set 2 are up shifted by two bits, so that the next byte can be used to generate the output during the next clock period. Note that because of the data order within the registers, up-shifting by two bits corresponds to up shifting by one byte. The output of CLB A is tied to long lines just above and below it, as shown in Figure 3-14. The outputs of the CLBs B, C and D are tied to the long lines as shown in Figure 3-14. The enables to the long lines are controlled using a state machine. Set 2 registers can be used to form four output words. In the mean time four new words have been written into set 1 registers. So, the next four words use the data from set 1 and set 2 will be filled with input words in the mean time.

The enables for latching the input will ping-pong between set 1 and set 2 registers. The output enables will also ping-pong between set 1 and set 2 registers. When the input is enabled to set 1 registers, the output of set 2 registers will be enabled. The maximum vertical distance for any net is 4 CLBs to connect to the horizontal long lines. Two controls are required to perform byte interleaving. A

parallel load/upshift control, which would enable a set of registers to either buffer input data or use the buffered data to form interleaved data at the output. The second control is used to enable the tri-state buffers of one of the sets.

HEC is calculated on the interleaved word using an 8 bit parallel HEC calculation circuit. This implementation uses 5 columns. To insert the path overhead word or the SONET overhead, the clocks to all the registers are masked.

#### 3.6 Summary

The 12.8 ns clock designs for both the STS-12c and the 4 x STS-3c transmitters have been verified by simulating the RTL VHDL model using Mentor Graphics tools. Modula-3 code was written to map the designs into Xilinx XC3195 chips and generate the Xilinx design files. The maximum delay through any net in the STS-12c transmitter Chip1 was found to be 12.0 ns. The maximum delay through a net in the 4 x STS-3c transmitter Chip1 was also 12.0 ns.

## Chapter 4

### Receiver Architecture

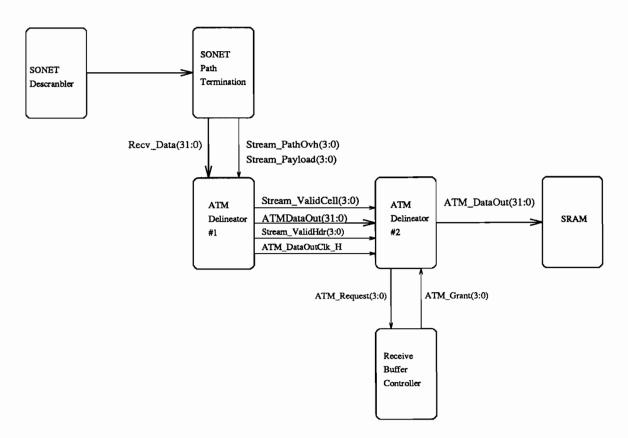

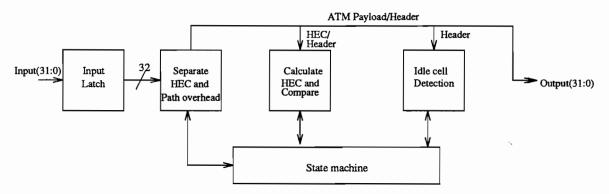

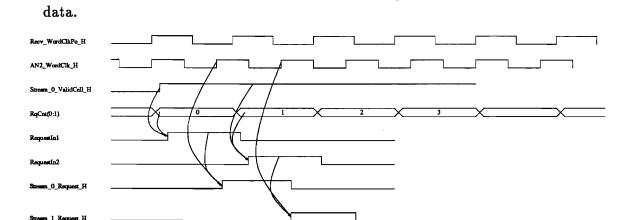

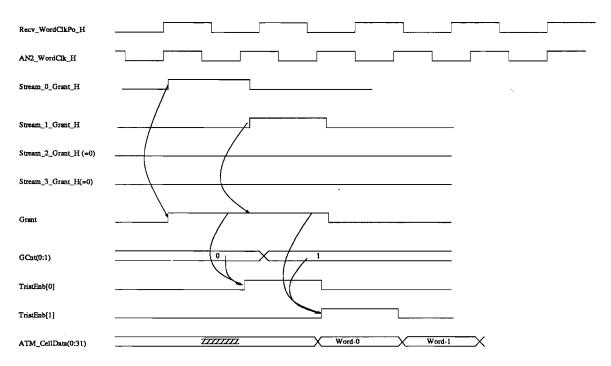

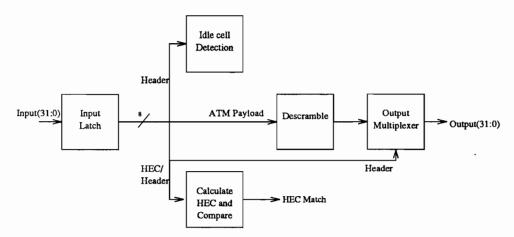

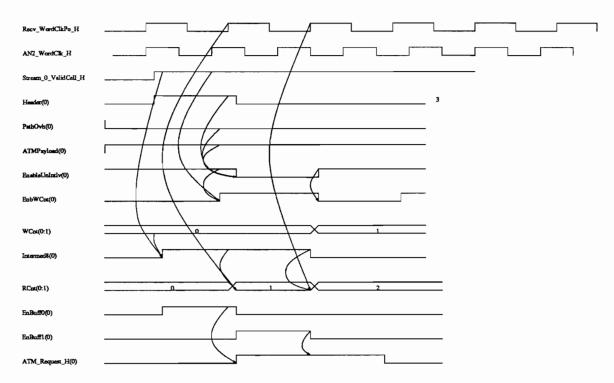

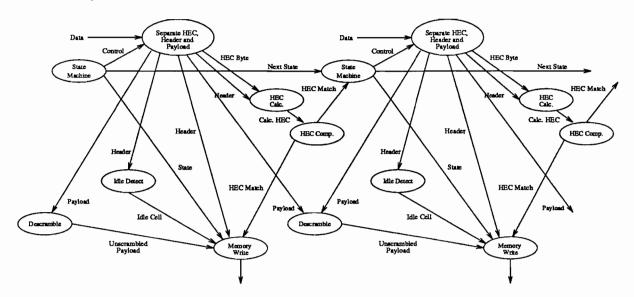

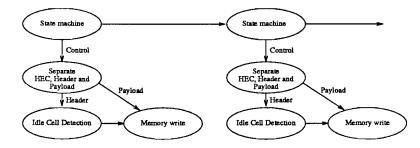

The ATM delineators use two Xilinx XC-3195 chips. A block diagram of the delineators in the receive section of the gateway card is shown in Figure 4-1. The first delineator gets the input data from the Path termination chip. It gets the control signals  $Stream_Payload(3:0)$  and  $Stream_PathOvh(3:0)$  from the Path termination chip. The signals  $Stream_Payload(3:0)$  indicate the presence of valid payload in the input data. The  $Stream_PathOvh(3:0)$  signals indicate that the path overhead byte is present in bits (7:0) of the next input word. For the STS-12c mode, only bits  $Stream_Payload(0)$  and  $Stream_PathOvh(0)$  are used.

The first delineator asserts  $Stream\_ValidCell(3:0)$  signals when the cell it processed has a valid HEC and it is not an idle cell. It asserts the  $Stream\_ValidHdr(3:0)$  signals to the second chip when a valid header is transferred. For the STS-12c mode, only signals  $Stream\_ValidCell(0)$  and  $Stream\_ValidHdr(0)$  are used.

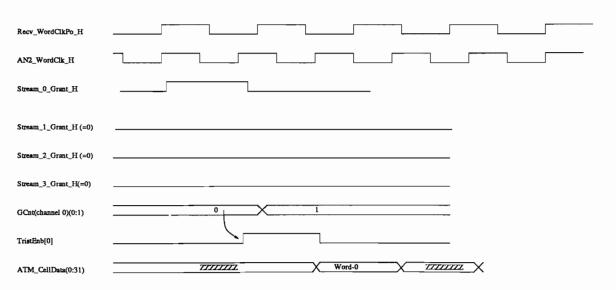

The data output of the first chip is the input to the second delineator chip. The data is clocked out of the first chip using the ATM\_DataOutClk in the STS-12c mode. The output data from Chip1 is written to the SRAM for further processing. Chip2 sends a request to write to the Receive Buffer Controller by asserting one of the ATM\_Request(3:0) signals when it wants to write to the SRAM.

Figure 4-1: System block diagram of the Receiver.

When it gets a grant on the corresponding  $ATM_{-}Grant(3:0)$  from the Receive Buffer Controller, it outputs the data.

Behavioral models, schematics and FPGA layouts of the receiver chips are given in Appendix E for the STS-12c mode and in Appendix F for the 4 x STS-3c mode. The simulation results of the transmitter and receiver connected together are given in Appendix C for the STS-12c mode and in Appendix D for the 4 x STS-3c mode. The simulation results and FPGA layout for the STS-12c design using 51.44 ns clock is given in Appendix G. This design was directly implemented in by writing Modula-3 code.

The STS-12c receiver design using 51.44 ns clock and the 4 x STS-3c designs were simulated using the VHDL code derived from Modula-3 code. All of these designs were simulated by connecting Chip1, Chip2 and the Receive Buffer Controller. These results are given in Appendix H.

#### 4.1 Functions of ATM Delineators

The functions of the ATM Delineators are:

- synchronize with the input data to delineate ATM cells,

- compute and compare the HECs of each incoming ATM cell,

- discard cells with incorrect HECs,

- detect and discard idle cells,

- discard the HEC byte and the Path overhead byte so that the output stream can be re-ordered as contiguous 32 bit words,

- re-arrange the ATM header bits as required by the AN2 crossbar,

- de-interleave the input to form a 32 bit word for each of the four channels in STS-3c mode.

#### 4.2 Architecture for the STS-12c mode

#### 4.2.1 Datapath of ATM Delineator Chip1

A parallel architecture is used to implement the STS-12c ATM cell delineation function. Chip1 performs all of the functions listed earlier. An ATM cell in the SRAM occupies thirteen 32 bit words. The organization of the data within the SRAM is similar to the organization of the data within the transmit FIFOs. The organization of data in the transmit FIFOs is shown in Figure 3-2.

Figure 4-2: Functional block diagram of STS-12c ATM Delineator - Chip1.

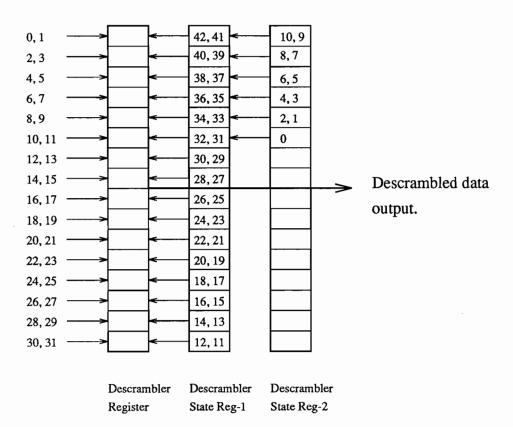

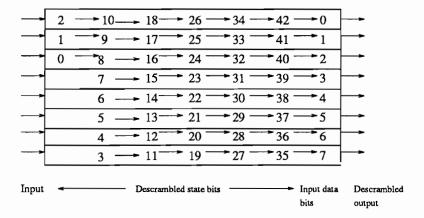

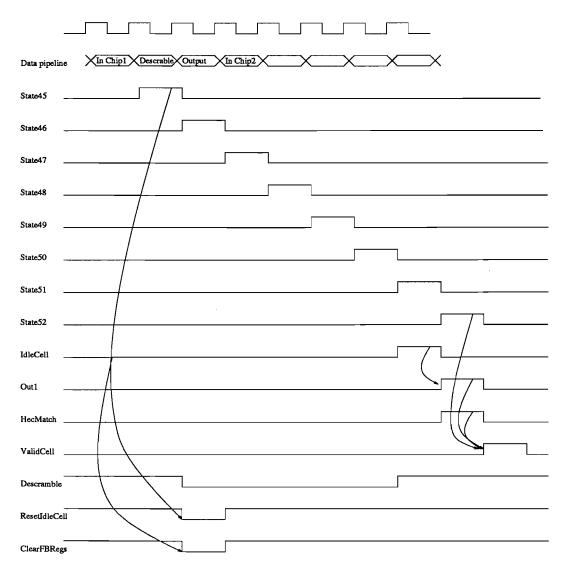

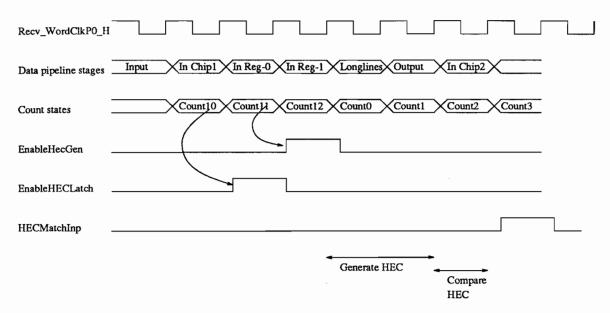

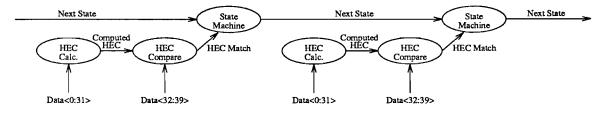

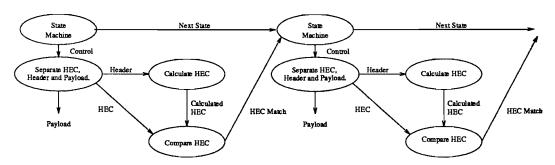

A functional block diagram illustrating the data flow through this chip is shown in Figure 4-2. The input data is latched at the IOBs. The input data is read using Recv\_WordClkP0\_H clock, which is a 51.44 ns clock. Next, the data is formatted to separate the HEC byte or the path overhead byte from the input data stream. HEC is computed on the input header word and compared with the input HEC byte. Next, the ATM cell payload is descrambled. Idle cell detection is done by comparing the input header word with the bit pattern of an idle cell header. Chip1 outputs a complete ATM cell in thirteen 32 bit words. The HEC byte, path overhead byte and the SONET overhead are discarded from the ATM cell before the data is output. The output data clock has a period of 51.44 ns, normally. When the HEC byte or the path overhead byte is discarded, the output clock period is 64.3 ns. The output clock is called ATM\_DataOutClk\_H from here on.

No data is output when SONET overhead is at the input of the chip.

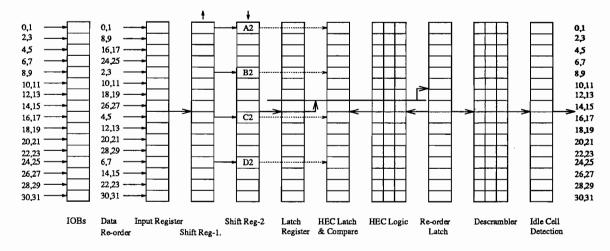

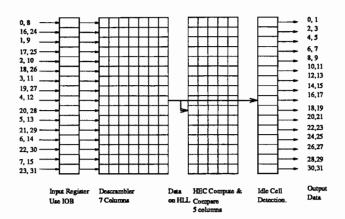

The Xilinx XC3195 floor plan of the chip's data path is shown in Figure 4-3.

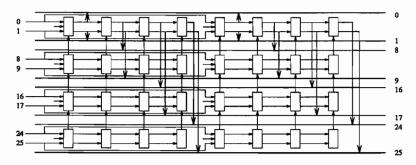

The input, which is 32 bits wide, is latched in the input pads using a 51.44 ns clock. The input data is re-ordered and latched by the *Input Register* column. The data order is as shown in Figure 4-3. The re-ordering is necessary to localize the interconnections in *ShiftReg-1* and *ShiftReg-2*. By using this order, the entire word can be shifted up or down by 8 bits by just moving the bits up or down by one CLB. This is explained next.

Figure 4-3: STS-12c ATM Delicator - Chip1.

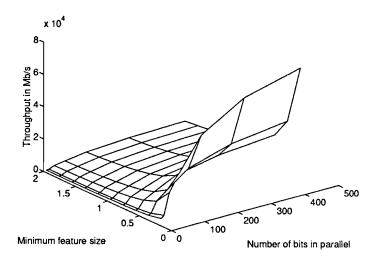

The output of the *Input Register* column is latched by *ShiftReg-1*. The data in *ShiftReg-1* are upshifted by 2 bits every 12.86 ns, which is one fourth of the 51.44 ns rate at which the input is latched. The 12.86 ns clock is called ByteClk. Using the ByteClk, 8 bits are shifted right to the *ShiftReg-2*, as shown in Figure 4-3. In this figure, the eight bits are shifted right from *ShiftReg-1* to CLBs A2, B2, C2 and D2 of *ShiftReg-2*. The data in *ShiftReg-2* is also shifted down using the ByteClk. An illustration of the operation of *ShiftReg-1* and *ShiftReg-2* is shown in Figure 4-4.