# Design and Implementation of a Link Level Adaptive Software Radio

**Richard A. Killoy**

B.S.E.E., University of Kansas, Lawrence, Kansas 1997

Submitted to the Department of Electrical Engineering and Computer Science and the Faculty of the Graduate School of the University of Kansas in partial fulfillment of the requirements for the degree of Masters of Science.

Professor in Charge

**Committee Members**

Date Thesis Accepted

## **Acknowledgements**

The success of this research relies heavily on the contributions made by my colleagues. This project is being implemented as part of the RDRN project at the University of Kansas. As such, many individuals have contributed to the design, planning, building and testing of this radio. I would be in error if I did not take a few moments to point out the significant contributions made by the myriad of people who have helped me along the way.

I would like to thank Professor Glenn Prescott for his guidance, his technical expertise and for giving me the chance to work on such a challenging project. Above all else, thanks for talking me into going to graduate school now as opposed to later.

All the classes I've taken pale in comparison to the knowledge I've learned from Ken Filardo. Your technical wisdom, your friendship, and above all else, your patience has helped to show me what real engineering and teamwork are all about.

To Shane Haas and Craig Sparks, the teamwork and knowledge we have shared the past two years has meant the world to me. I can only hope I work with other engineers as personable and knowledgeable as you. I still think the potato gun was our best work yet.

The RF expertise and helpfulness of Dan Depardo was crucial to the success of this project. Thank you for all your time and patience.

Above all else, thanks go to my fiancée, Lorie. Thank you so much for all your support and patience while I've written this. You've done all the little things that make my life so much easier while working on this. They are too numerous to name here, but thanks just for being there. Now, finally, we can start our life together.

### **Abstract**

Over the past few years, the software radio has emerged from research as a commercially viable and flexible digital communication system. Advances in digital technology are quickly making the software radio an attractive strategy for low-cost, multi-dimensional transceivers. A needed function in tomorrow's transceivers is the ability to change, or adapt, to the rapidly changing channels (fading channels) encountered in wireless communication systems. This paper centers around the design and implementation of such a system, a flexible software controlled radio, adaptive at both the physical and data-link layers. The microprocessor driven radio described herein is a communications and data acquisition platform which supports multiple modulation formats, varying data rates and adaptive Forward Error Correction (FEC). This provides a means for developing algorithms to control radio parameters in the face of rapidly changing channels. We have also provided a means for examining and storing the digital symbols received across the channel. These stored symbols are used to verify adaptive channel estimation algorithms offline. From these channel parameters (i.e., Doppler spread, coherence bandwidth) software radios can dynamically change their characteristics to best suit the constantly changing channel.

## **Table of Contents**

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                     | II                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <u>ABSTRACT</u>                                                                                                                                                                                                                                                                                                                                      | III                                                                                    |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                    | IV                                                                                     |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                      | VI                                                                                     |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                       | VII                                                                                    |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                               | 1                                                                                      |

| Brief Overview of the RDRN2 Project<br>RDRN2 Communication Systems Overview                                                                                                                                                                                                                                                                          |                                                                                        |

| CHAPTER 2 BACKGROUND                                                                                                                                                                                                                                                                                                                                 | 7                                                                                      |

| SUPER-HETERODYNE RECEIVER<br>DIGITAL RADIOS & SOFTWARE RADIOS<br>Digital IF and Subsampling Receivers<br>Decimation<br>TRANSCEIVER PERFORMANCE METRICS                                                                                                                                                                                               |                                                                                        |

| CHAPTER 3 SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| TRANSMITTER REQUIREMENTS<br>RECEIVER REQUIREMENTS<br>MULTIPLE ACCESS SCHEME AND BANDWIDTH UTILIZATION<br>LINK BUDGET<br>POWER REQUIREMENTS<br>THE CONTROL BUSSES                                                                                                                                                                                     | 24<br>26<br>29<br>32<br>36                                                             |

| <u>CHAPTER 4</u> TRANSMITTER IMPLEMENTATION                                                                                                                                                                                                                                                                                                          |                                                                                        |

| Baseband to IF         Input Stage & Formatting         RC Filters         IF to RF         Quadrature Modulator         240 MHz PLL and VCO Carrier Generation         Amplification and SAW Filter         Programmable Attenuators         RF Section         Mixer         LO Generation         RF Mixer         RF Amplification and Filtering | 42<br>42<br>43<br>43<br>43<br>44<br>45<br>46<br>46<br>46<br>47<br>48<br>48<br>48<br>48 |

| Quad-Sectored Patch Antenna Array                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| CHAPTER 5 RECEIVER IMPLEMENTATION<br>Signal Level Table<br>Noise Figure Graph<br><i>RF Receiver</i>                                                                                                                                                                                                                                                  |                                                                                        |

| Patch Antenna sub-Assembly                                                                                                                                                                                                                                          |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RF Mixer                                                                                                                                                                                                                                                            |          |

| LO Generation                                                                                                                                                                                                                                                       |          |

| IF to ADC                                                                                                                                                                                                                                                           |          |

| Low Pass Filter and Amplification Section                                                                                                                                                                                                                           |          |

| SAW Filter                                                                                                                                                                                                                                                          |          |

| AGC Amplifier                                                                                                                                                                                                                                                       |          |

| IF Amplification Chain                                                                                                                                                                                                                                              |          |

| ADC to Baseband                                                                                                                                                                                                                                                     |          |

| ADC Input Conditioning                                                                                                                                                                                                                                              |          |

| Analog to Digital Converter (ADC)                                                                                                                                                                                                                                   |          |

| Signal Processing1 Altera                                                                                                                                                                                                                                           |          |

| Digital Quadrature Tuner, the HSP50110                                                                                                                                                                                                                              |          |

| Signal Processing2 Altera                                                                                                                                                                                                                                           |          |

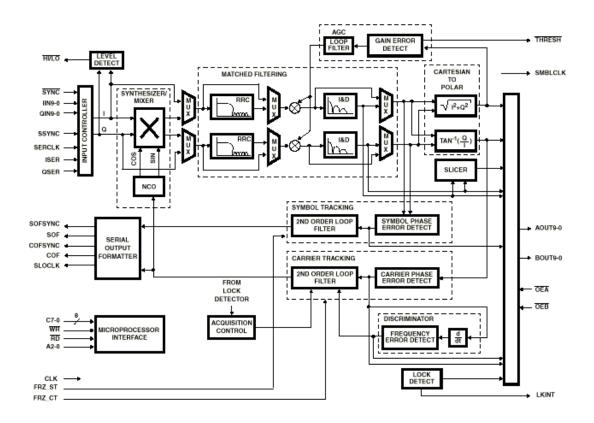

| Digital Costas Loop, the HSP50210                                                                                                                                                                                                                                   |          |

| CHAPTER 6 SUMMARY AND CONCLUSIONS                                                                                                                                                                                                                                   | 60       |

|                                                                                                                                                                                                                                                                     |          |

| FUTURE WORK                                                                                                                                                                                                                                                         |          |

| REFERENCES                                                                                                                                                                                                                                                          |          |

|                                                                                                                                                                                                                                                                     |          |

| APPENDIX A                                                                                                                                                                                                                                                          |          |

| Jumper Settings & Headers                                                                                                                                                                                                                                           |          |

| JUMPER OF LINUS & FIEADERS                                                                                                                                                                                                                                          |          |

|                                                                                                                                                                                                                                                                     |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS                                                                                                                                                                                                                       | 77       |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS                                                                                                                                                                                               | 77<br>79 |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET                                                                                                                                                             |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS                                                                                                                                                                                               |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS                                                                                                                                    |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B                                                                                                                      |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B<br><br>RF SCHEMATICS                                                                                                 |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B<br>RF SCHEMATICS<br>IF AND DIGITAL SECTION SCHEMATICS                                                                |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B<br><br>RF SCHEMATICS                                                                                                 |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B<br>RF SCHEMATICS<br>IF AND DIGITAL SECTION SCHEMATICS<br>ALTERA CPLD COMBINATION LOGIC DIAGRAMS<br>BILL OF MATERIALS |          |

| CONNECTOR DESCRIPTION AND INPUT/OUTPUT LEVELS<br>PROGRAMMING THE PLLS<br>PROGRAMMING THE HARRIS CHIPSET<br>PROGRAMMING THE CPLDS<br>APPENDIX B<br>RF SCHEMATICS<br>IF AND DIGITAL SECTION SCHEMATICS<br>ALTERA CPLD COMBINATION LOGIC DIAGRAMS                      |          |

## **List of Figures**

| FIGURE 1 – RDRN SYSTEM ARCHITECTURE                                                | 4    |

|------------------------------------------------------------------------------------|------|

| FIGURE 2 - BLOCK FUNCTIONALITY OF A DIGITAL COMMUNICATION SYSTEM                   | 7    |

| FIGURE 3 – EXAMPLE OF NONLINEARITIES IN A POWER AMPLIFIER                          | 9    |

| FIGURE 4 – SUPER-HETERODYNE ARCHITECTURE                                           | . 10 |

| FIGURE 5 – TYPICAL SOFTWARE RADIO                                                  | . 14 |

| FIGURE 6 – DETAILED VIEW OF THE DIGITAL SECTION OF A SOFTWARE RADIO                | . 16 |

| FIGURE 7 – SUB-SAMPLING AT THE IF                                                  | . 17 |

| FIGURE 8 – ALIASING EFFECTS OF DECIMATION                                          | . 18 |

| FIGURE 9 – TRANSMITTER BLOCK DIAGRAM                                               | 23   |

| FIGURE 10 – RECEIVER BLOCK DIAGRAM                                                 | 25   |

| FIGURE 11 – SPECTRUM UTILIZATION AND CHANNEL ASSIGNMENT                            |      |

| FIGURE 12 – COMPLETED RDRN2 RADIO, INCLUDING HOUSING                               | 28   |

| FIGURE 13 – RADIO INTERCONNECT BLOCK DIAGRAM                                       |      |

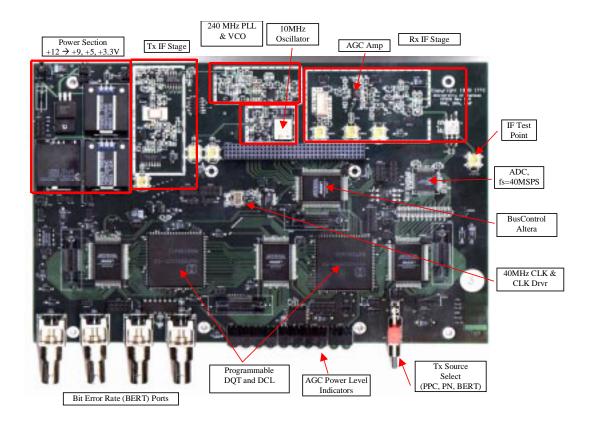

| FIGURE 14 – DIGITAL AND IF SUBSECTION                                              | 34   |

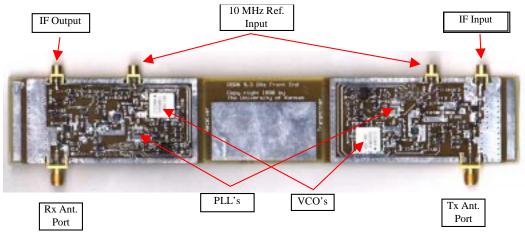

| FIGURE 15 – 5.3 GHz RF FRONT END.                                                  | . 35 |

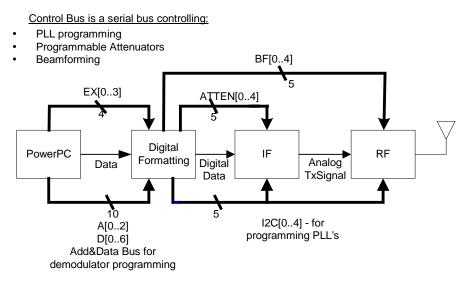

| FIGURE 16 – RADIO SECTIONS AND BUS CONNECTIVITY                                    | 36   |

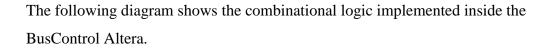

| FIGURE 17 – BUSCONTROL ALTERA INTERNAL LOGIC DIAGRAM                               | . 38 |

| FIGURE 18 - COMBINATION LOGIC IMPLEMENTED BY I2CBUS, INTERNAL TO BUSCONTROL ALTERA | . 39 |

| FIGURE 19 – TRANSMITTER BLOCK DIAGRAM, BASEBAND TO IF                              |      |

| FIGURE 20 – CLOSE-UP VIEW OF TRANSMIT IF SECTION                                   | . 41 |

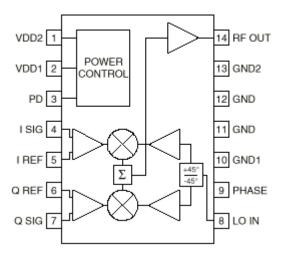

| FIGURE 21 – RF2464 MODULATOR                                                       | 43   |

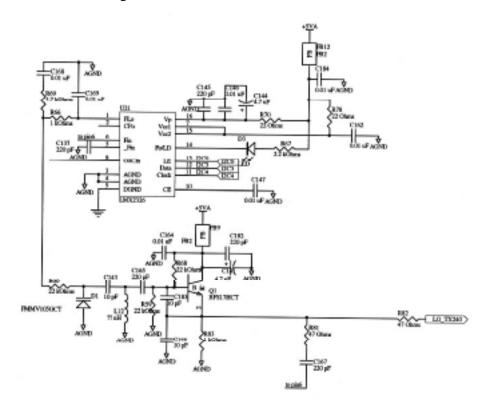

| FIGURE 22 – 240MHz PLL AND VCO                                                     | 44   |

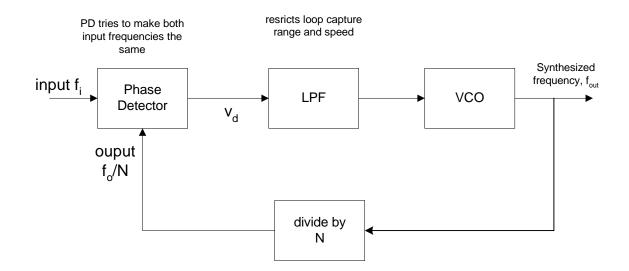

| FIGURE 23 – PLL USED AS FREQUENCY SYNTHESIZER                                      | 45   |

| FIGURE 24 – TRANSMITTER BLOCK DIAGRAM, IF THRU RF SECTION                          | .46  |

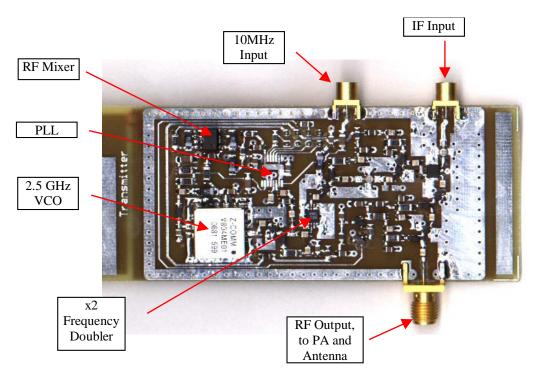

| FIGURE 25 – CLOSE-UP VIEW OF THE RF TRANSMITTER STAGE                              |      |

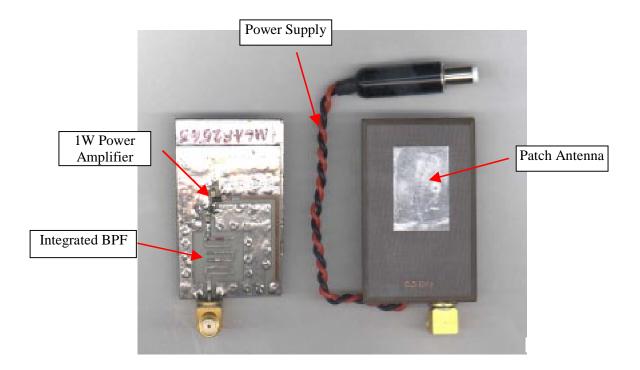

| FIGURE 26 – INTEGRATED TRANSMIT PATCH AND POWER AMPLIFIER                          | . 50 |

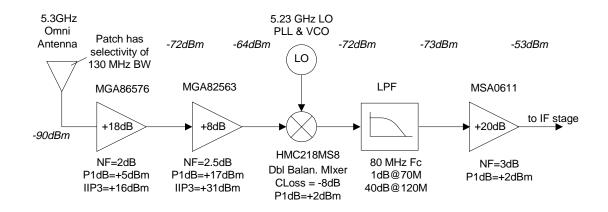

| FIGURE 27 – RECEIVER BLOCK DIAGRAM (RF TO IF)                                      | . 51 |

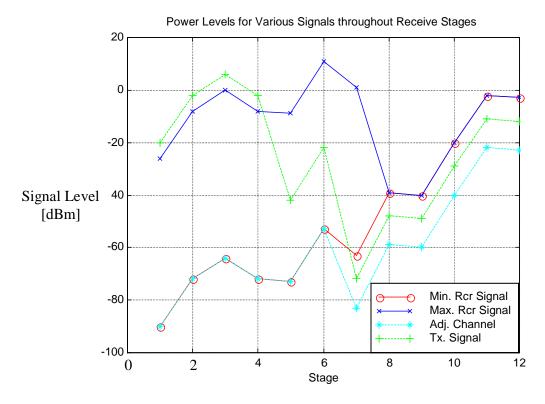

| FIGURE 28 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN                  | . 52 |

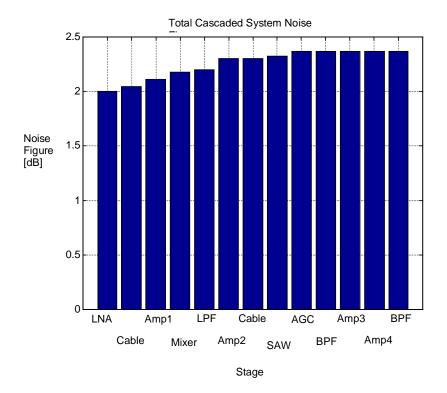

| FIGURE 29 – NOISE FIGURE THROUGHOUT SYSTEM                                         | . 53 |

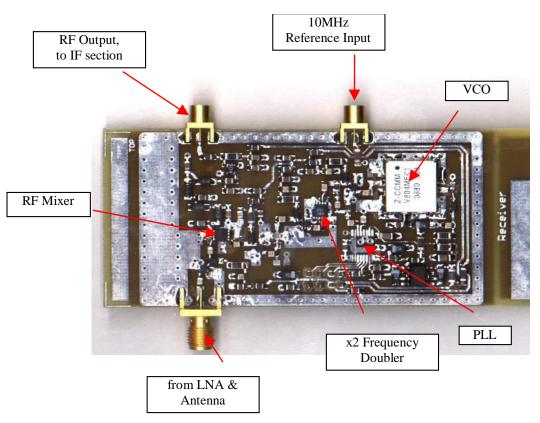

| FIGURE 30 - CLOSE-UP VIEW OF RF RECEIVE SECTION                                    | . 56 |

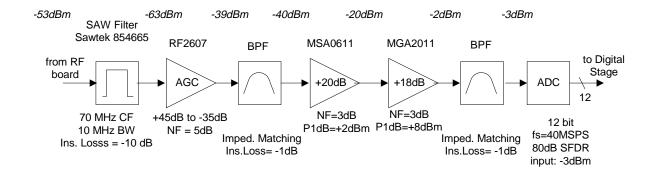

| FIGURE 31 – RECEIVER BLOCK DIAGRAM (IF TO DIGITAL)                                 | . 57 |

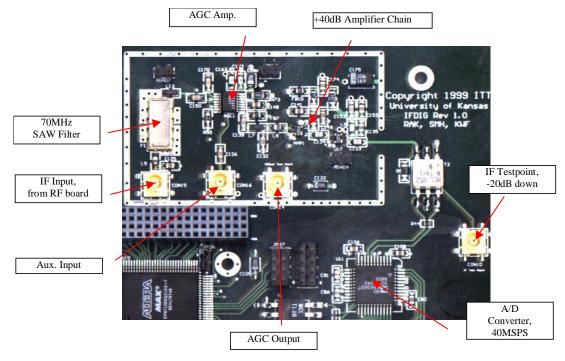

| FIGURE 32 – CLOSE-UP VIEW OF RECEIVER IF STAGE                                     | . 58 |

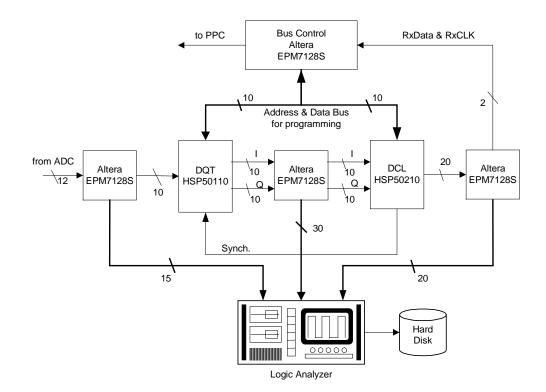

| FIGURE 33 – RECEIVER BLOCK DIAGRAM (BASEBAND)                                      | . 62 |

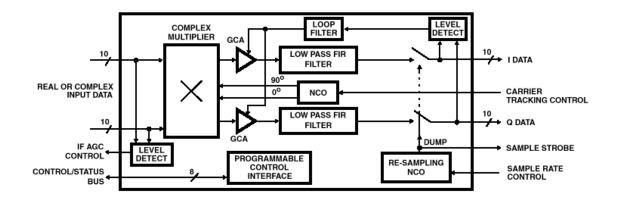

| FIGURE 34 - HSP50110 DIGITAL QUADRATURE TUNER                                      | . 63 |

| FIGURE 35 – FUNCTIONAL BLOCK DIAGRAM OF HSP50110                                   | . 64 |

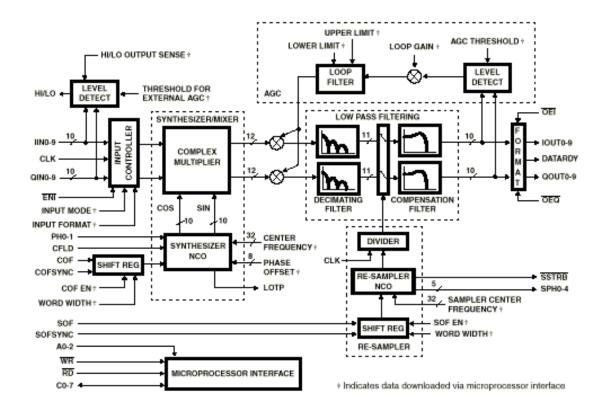

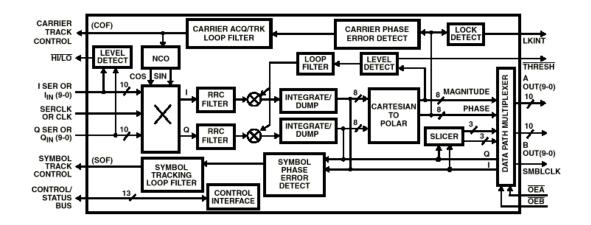

| FIGURE 36 - HSP50210 DIGITAL COSTAS LOOP                                           | . 66 |

| FIGURE 37 – FUNCTIONAL BLOCK DIAGRAM OF HSP50210                                   | . 67 |

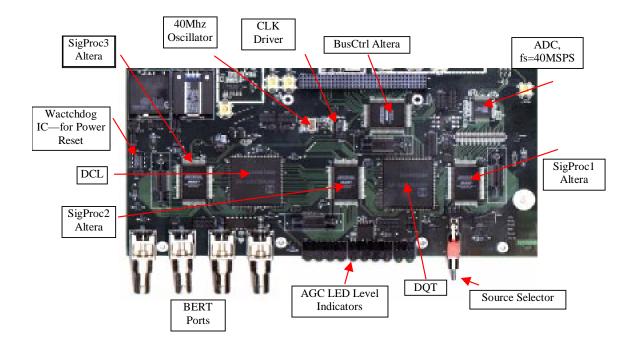

| FIGURE 38 – CLOSE-UP VIEW OF RECEIVER DIGITAL SECTION                              | . 68 |

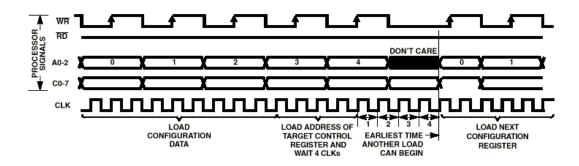

| FIGURE 39 – CONTROL REGISTER LOADING SEQUENCE                                      | . 83 |

## **List of Tables**

| TABLE 2 - DYNAMICALLY ADJUSTABLE RADIO PARAMETERS.6TABLE 3 - TRANSMITTER REQUIREMENTS.22TABLE 4 - RECEIVER REQUIREMENTS.24TABLE 5 - LINK BUDGET FOR 5.3GHZ LINK.31TABLE 6 - POWER REQUIREMENTS FOR VARIOUS SECTIONS32TABLE 7 - TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF41TABLE 8 - TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES47TABLE 9 - RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN52TABLE 10 - JUMPER SETTINGS74TABLE 11 - CONNECTOR DESCRIPTION77TABLE 12 - CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF80TABLE 13 - 240 MHZ PLL PROGRAMMING80TABLE 14 - WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE82TABLE 15 - PROGRAMMING DATA FOR HARRIS CHIPSET83 | TABLE 1 – RDRN GOALS AND SOLUTION STRATEGIES EMPLOYED                | 5  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----|

| TABLE 4 - RECEIVER REQUIREMENTS.24TABLE 5 - LINK BUDGET FOR 5.3GHZ LINK31TABLE 6 - POWER REQUIREMENTS FOR VARIOUS SECTIONS32TABLE 7 - TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF41TABLE 8 - TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES47TABLE 9 - RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN52TABLE 10 - JUMPER SETTINGS74TABLE 11 - CONNECTOR DESCRIPTION77TABLE 12 - CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF80TABLE 13 - 240 MHZ PLL PROGRAMMING80TABLE 14 - WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE82                                                                                                                                          | TABLE 2 – DYNAMICALLY ADJUSTABLE RADIO PARAMETERS.                   | 6  |

| TABLE 5 – LINK BUDGET FOR 5.3GHZ LINK31TABLE 6 – POWER REQUIREMENTS FOR VARIOUS SECTIONS32TABLE 7 – TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF41TABLE 8 – TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES47TABLE 9 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN52TABLE 10 – JUMPER SETTINGS74TABLE 11 – CONNECTOR DESCRIPTION77TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF80TABLE 13 – 240 MHZ PLL PROGRAMMING80TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE82                                                                                                                                                                            | TABLE 3 – TRANSMITTER REQUIREMENTS                                   |    |

| TABLE 6 – POWER REQUIREMENTS FOR VARIOUS SECTIONS32TABLE 7 – TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF41TABLE 8 – TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES47TABLE 9 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN52TABLE 10 – JUMPER SETTINGS74TABLE 11 – CONNECTOR DESCRIPTION77TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF80TABLE 13 – 240 MHZ PLL PROGRAMMING80TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE82                                                                                                                                                                                                                   | TABLE 4 – RECEIVER REQUIREMENTS                                      | 24 |

| TABLE 7 – TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF       41         TABLE 8 – TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES       47         TABLE 9 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN       52         TABLE 10 – JUMPER SETTINGS       74         TABLE 11 – CONNECTOR DESCRIPTION       77         TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF       80         TABLE 13 – 240 MHz PLL PROGRAMMING       80         TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE       82                                                                                                                                               | TABLE 5 – LINK BUDGET FOR 5.3GHZ LINK                                |    |

| TABLE 8 – TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES       47         TABLE 9 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN       52         TABLE 10 – JUMPER SETTINGS       74         TABLE 11 – CONNECTOR DESCRIPTION       77         TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF       80         TABLE 13 – 240 MHz PLL PROGRAMMING       80         TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE       82                                                                                                                                                                                                                   | TABLE 6 – POWER REQUIREMENTS FOR VARIOUS SECTIONS                    |    |

| TABLE 9 – RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN       52         TABLE 10 – JUMPER SETTINGS       74         TABLE 11 – CONNECTOR DESCRIPTION       77         TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF       80         TABLE 13 – 240 MHz PLL PROGRAMMING       80         TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE       82                                                                                                                                                                                                                                                                                                | TABLE 7 – TRANSMIT SIGNAL LEVEL FOR BASEBAND TO IF                   | 41 |

| TABLE 10 – JUMPER SETTINGS74TABLE 11 – CONNECTOR DESCRIPTION77TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF80TABLE 13 – 240 MHz PLL PROGRAMMING80TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE82                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TABLE 8 - TRANSMIT OUTPUT SIGNAL LEVELS FOR IF TO RF STAGES          | 47 |

| TABLE 11 – CONNECTOR DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TABLE 9 - RECEIVE SIGNAL LEVELS AT VARIOUS SECTIONS OF RX CHAIN      |    |

| TABLE 12 – CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF       80         TABLE 13 – 240 MHz PLL PROGRAMMING       80         TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE       82                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TABLE 10 – JUMPER SETTINGS                                           | 74 |

| TABLE 13 – 240 MHz PLL PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TABLE 11 – CONNECTOR DESCRIPTION.                                    | 77 |

| TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE    82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TABLE 12 - CHANNEL PLAN AND FREQUENCY PROGRAMMING INFORMATION FOR RF | 80 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TABLE 13 – 240 MHz PLL PROGRAMMING                                   | 80 |

| TABLE 15 - PROGRAMMING DATA FOR HARRIS CHIPSET    83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TABLE 14 – WRITE ADDRESS MAP FOR MICROPROCESSOR INTERFACE            |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TABLE 15 - PROGRAMMING DATA FOR HARRIS CHIPSET                       |    |

### <u>Chapter 1</u> Introduction

The purpose of this research is to develop a high-speed, wireless, Asynchronous Transfer Mode (ATM) transceiver. This transceiver is a digitally controlled software radio, adaptive at both the physical and data-link layers. This receiver is being designed and implemented in conjunction with the Rapidly Deployable Radio Network Project (RDRN) at the University of Kansas.

The goal of this transceiver is to provide physical layer functionality along with link layer adaptivity for a self-configurable, wireless ATM network.

The goal of the RDRN project is to design a high-speed, wireless ATM communication system that is adaptive at both the network and data-link layers to allow for rapid deployment and for use in a changing environment. Also, RDRN hopes to create architectures, protocols, and prototype hardware and software for a high-speed (1-8 Mb/s at 10 km), wireless IP/ATM network, based on Global Positioning System (GPS) location information that can be deployed rapidly in areas of military conflicts or civilian disasters where communication infrastructures are lacking and/or destroyed.

#### **Brief Overview of the RDRN2 Project**

The RDRN project has been an ongoing research program at the University of Kansas for several years. It has concentrated on the development and requirements needed for the rapid deployment of communication networks. The need for Quality of Service (QoS) support and seamless integration with commercial networks has led to an approach that uses wireless technology for the communications links, and ATM for networking.

This second phase of research, RDRN2, builds upon the earlier success of RDRN1. For this phase, our research teams have been concentrating on the following areas:

- <u>Channel Estimation and Link Adaptation</u>. We are continuing our work on algorithms to estimate and adapt to rapidly changing channels, such as those encountered in mobile networks (i.e., Rayleigh fading channels). Also, we are developing algorithms to estimate the channel state and use that information to change power level, modulation, FEC, and/or frame length. This work will result in a control algorithm for adapting to link characteristics.

- 2) <u>Software Radios</u>. We have built single, full-duplex, point-to-point radios based on the RDRN2 year one radio to test, evaluate, and validate the channel estimation and link adaptation algorithms stated above. These radios incorporate a modular RF section, and we will test and validate the channel estimation and link adaptation algorithms at 5.3 GHz, 2.4 GHz, and 1.2 GHz.

- 3) <u>Adaptive Networking</u>. RDRN is developing a flowspec tailored to mobile networks. The flowspec will facilitate the mapping of IP and ATM service classes across mobile networks and coordinate switching at the frame, ATM, and IP layers. We also studied the performance of multilayer networks (e.g., multi-hop, short distance, peer-to-peer at lower echelons, longer hop, switched at higher echelons).

- 4) <u>Resource Reservation Styles</u>. Evaluation of resource reservation styles for rapidly mobile networks. This evaluation will determine features of the current styles for mobile networks in light of the available knowledge such as accurate timing and position information as well as network-aware applications.

- 5) <u>Comparative Performance Evaluation of IP versus ATM</u>. Evaluation of the comparative performance of IP and ATM for high mobility networks

as a function of the link capacity versus the mix of traffic (delay/jitter sensitive and non-delay/jitter sensitive). This evaluation was carried out in an emulated environment using the RDRN software ATM switch on up to 24 nodes.

The focus of this paper centers around the first two items stated above. Mainly, the building of a software radio for use in channel estimation which is adaptive at the physical and data-link layers.

#### **RDRN2** Communication Systems Overview

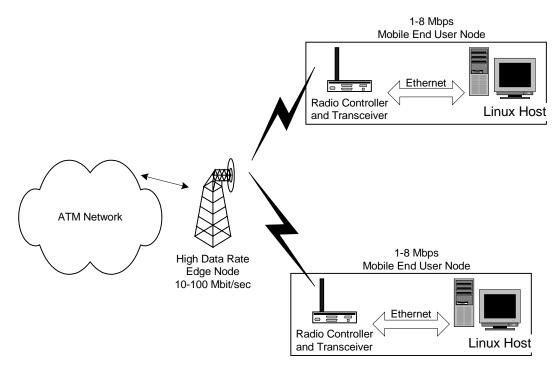

RDRN is made up of two types of communication nodes: 1) end user nodes, providing wireless ATM access for users at a rate of up to 8 Mbps; and 2) edge nodes which serve as Radio Access Points (RAPs) or base stations, and provide switching and connectivity between users. Both types of nodes contain GPS receivers for location determination, software-controlled radios using GPS-derived location information and network control software. [9]

The edge nodes also have integral ATM (software) switches, and they are interconnected by high-capacity (10 to 155 Mbps), directional radio links. Edge nodes can also interface to wired ATM networks.

The RDRN architecture consists of three overlaid radio networks:

- a low bandwidth, low power, omni-directional orderwire packet radio network for broadcasting location information and for network configuration and management;

- (2) a cellular-like ATM radio network for end-user access to edge nodes with handoffs; and

- (3) a high-capacity, wireless ATM backbone network providing connection between switches, using high-capacity radios with multiple directional beams.

This paper focuses on the design and implementation of the end user nodes. Their main function is to provide wireless ATM access to the edge nodes at data rates from 1-8 Mbps. The following diagram depicts the system setup configuration for the RDRN system.

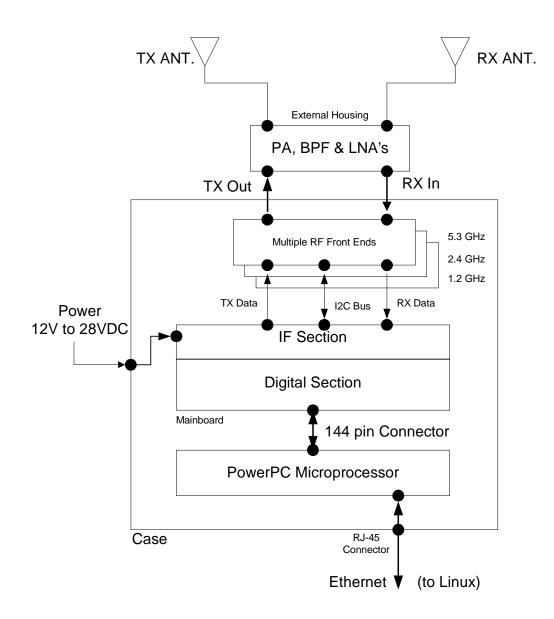

Figure 1 – RDRN System Architecture

This paper focuses on the design of the radio controller and the transceiver. These two devices perform all of the Physical Layer and Data-Link Layers functions for our communication system.

During the design phase, we considered many alternatives to implement our software radios. Our major concern was being able to accomplish the goals RDRN set out to achieve.

| Goal                                   | Solution Strategy Employed                  |

|----------------------------------------|---------------------------------------------|

| Channel Estimation Algorithms          | The use of adaptive equalization,           |

|                                        | functioning as channel estimators. Refer    |

|                                        | to the K.U. Masters thesis "Decision        |

|                                        | Weighted Adaptive Algorithms with           |

|                                        | Applications to Wireless Channel            |

|                                        | Estimation" by Shane Haas, April 1999.      |

| Link Level Adaptation                  | Software radio allows us the flexibility to |

|                                        | change link level parameters. Table 2,      |

|                                        | next page, shows the parameters which       |

|                                        | are dynamically changeable.                 |

| Radios to Test, Evaluate, and Validate | Software radios implementing the use of     |

| the channel estimation and link-level  | high-speed ADC and various DSP chips.       |

| algorithms                             | These chips can be programmed               |

|                                        | dynamically via a PowerPC processor.        |

Table 1 – RDRN Goals and Solution Strategies Employed

RDRN is adaptable to changes in the quality of the radio communication environment. While ATM is designed to operate on high-quality (almost error-free), wired links, typical radio links suffer higher bit error rates and the link quality changes as a function of time due to mobility and changes in the environment. By estimating the channel parameters, such as multipath spread and signal-to-noise ratio, communication parameters at the link and network levels can be adapted to provide appropriate throughput and quality of service. This is the goal of our software-radio based communication system.

The software radio provides us with the ability to dynamically change many characteristics of our radio "on-the-fly." This allows us to have link-level adaptation features and be able to support a myriad of modulation formats and bit rates. The following table depicts parameters which we have the ability to change.

| Adaptive Parameter                       | Allowable Values                         |  |

|------------------------------------------|------------------------------------------|--|

| RF Section                               |                                          |  |

| Transmit Power Control, TPC              | 5 dBm to 25 dBm in 2 dB increments       |  |

| Carrier Frequency                        | Carrier frequency can be tuned within RF |  |

|                                          | bandwidth in increments of 10 MHz        |  |

| *RF Front End                            | Static Design, but supports 5.3 GHz, 2.4 |  |

|                                          | GHz, and 1.2 GHz band.                   |  |

| Physical Layer                           |                                          |  |

| Modulation format                        | BPSK, QPSK                               |  |

| Data Rate                                | 1, 2, 4 MSPS                             |  |

| Data Link Layer                          |                                          |  |

| FEC                                      | Limited by complexity of combinational   |  |

|                                          | logic circuit implemented in Alteras     |  |

| Multiple Access Scheme                   | TDMA, FDMA or hybrid combination         |  |

|                                          | of both                                  |  |

| RF Preamble for TDMA                     | Limited by length of time slot           |  |

| HDLC Frame Length                        | Limited by Ethernet Packet Size, 1.5 kB  |  |

| * DE Front End is not dynamically adjust |                                          |  |

## Table 2 – Dynamically Adjustable Radio Parameters.

\* RF Front End is not dynamically adjustable. Must be manually switched in and out.

### <u>Chapter 2</u> Background

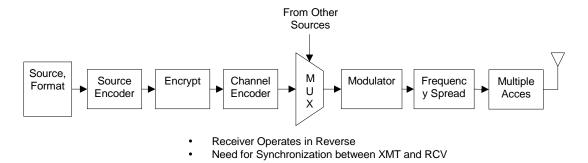

In any communication system, whether wireless or wired, a radio performs the functions depicted in Figure 2 below.

Figure 2 - Block Functionality of a Digital Communication System

While some functional blocks may not be needed in some systems, Figure 2 outlines the functionality of a generic radio system. The only blocks which need be present are the modulator/demodulator and the source. The question still remains, how best to implement these blocks to maximize information transfer.

The wireless communications environment, especially in urban areas, can be quite hostile. The interference, in and out of band, can be quite large, thereby imposing severe constraints upon the transceiver architecture. Each user in a wireless environment must share the resources the communication network has available. The most precious of these resources is the bandwidth each user is allocated. This limited bandwidth is directly related to how quickly information can be sent on the network.

Information theory, more specifically Shannon's Theorem, says the maximum amount of information that can be sent across a communication link with a given Signal to Noise Ratio (SNR) and bandwidth is:

$$c = W \log_2 \left[ 1 + SNR \right]$$

where c = channel capacity [bits/sec] W = transmitted bandwidth [Hz] SNR = received signal to noise ratio

Shannon's Theorem puts a theoretical maximum speed limit on the rate of information exchange. It is important to note, that although Shannon says we can achieve this capacity, he does not tell us how to achieve it. For this reason, most communication links are run at a bit rate below the Shannon limit.

The limited bandwidth available to each user impacts the design of the RF section. The transmitter must employ modulation, amplification and filtering such that it minimizes adjacent channel interference. The receiver, on the other hand, must be able to filter the desired band, filter the desired channel, and amplify it while minimizing the interference from strong neighboring channels.

One of the most important design parameters in any receiver is the overall system noise figure (NF). All components generate thermal noise, and this noise adds to, or corrupts, the signal we are trying to detect. Noise figure is a measure of the degradation in SNR as a signal propagates through a system. From Shannon's Theorem, above, we can see that more noise means less capacity.

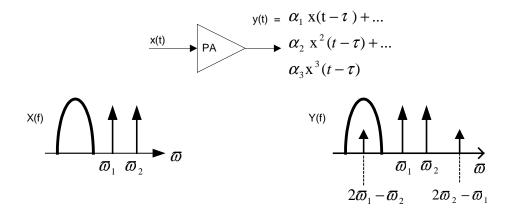

As we cascade components together in a receive chain, more and more thermal noise is generated, thereby adding to the overall system NF. It can be shown that the noise contributed by each stage decreases as the gain preceding the stage increases. This implies that the first few stages in a cascade are the most critical. Conversely, if a stage exhibits attenuation (loss), the noise figure of the following circuit is "amplified." Careful attention must be paid to the noise figures of these first components in a receive chain [4]. In modern receivers, low-noise amplifiers (LNA's) are typically used. These amplifiers typically have noise figures of only a few dB. Another important parameter to be considered in the design of any transceiver is the non-linearity of any component in the transmit and receive stage. Figure 3, below, depicts how nonlinearities can effect the transmitter performance. [15]

Figure 3 – Example of Nonlinearities in a Power Amplifier

It is important to note the nonlinear nature of the system. An ideal linear system will output a scaled, time-delayed version of its input. However, as shown in Figure 3, a nonlinear system will generate higher order products. These are called intermodulation products. While we may try to minimize this nonlinear behavior, it is always there to some degree.

Amplifiers and mixers in the transmit stage will often generate intermodulation products that fall out-of-band. These interferers can only be attenuated to a small degree by front end bandpass filters and therefore must be acceptably small by design. [15]

These product terms can be quite large and can be received in-band by the receiver. The nonlinear nature of mixers and amplifiers in the receiver front end becomes extremely important at this point. As shown above, odd-order nonlinearities can yield intermodulation products that fall within the desired channel.

Although distorting the amplitude, this effect is important even if the signal carries information only in its phase or frequency, because the zero-crossing points of the desired signal are corrupted by the intermodulation products.

Another important concern in the design of a transceiver is the dynamic range of the signals. A typical communications system operating in a fading environment experiences path loss such that the receiver requires a dynamic range greater than 90 dB. In systems with large dynamic range, crosstalk and input noise can become a problem. Also, the amount of isolation between the transmitter and the receiver becomes important. If the receiver is not sufficiently isolated from the transmitter, these interfering signals may have enough power to desensitize the LNA (for example, if the interferer is above the 1 dB compression point).

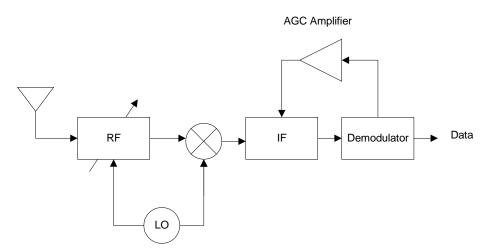

#### **Super-Heterodyne Receiver**

The most popular receiver architecture in use today, and the one used for the RDRN receiver, is the super-heterodyne receiver. Practically all receivers built today are of this type. A receiver's job is to perform carrier-frequency tuning (mixing), filtering and amplification, all while minimizing noise. The popularity of the super-heterodyne lies in the fact that it performs the first two of these functions in a simple and efficient manner. The following diagram depicts a system level diagram of a super-heterodyne receiver.

**Figure 4 – Super-Heterodyne Architecture**

If a receiver is to extract a narrow-band signal accompanied by large interferers from a relatively high frequency band, a bandpass filter with appreciable Q is needed. If a second-order LC filter is to provide 60 dB of attenuation at 45 kHz from the center, this is an equivalent Q on the order of  $10^7$ , a value difficult to achieve even in such filters as surface acoustic wave (SAW) devices. [15]

It is important to note that typical filters exhibit a trade-off between loss and Q. Consider also that a lossy circuit magnifies the noise figure of the following stage and you can see why wide bandwidth, low-loss filters are desired at the RF stage.

Attempting to extract the information band directly from the RF is not very practical. The super-heterodyne receiver first translates this large bandwidth down to a more manageable frequency before attempting to extract the narrow information bandwidth. This relaxes the Q required of the channel select filter.

In choosing the LO and IF frequencies, one must concern themselves with the problem of image. While each transceiver impose constraints upon its own signal emissions, it may no have control over signals in other bands.

The mixer will develop an IF output when the input signal frequency is greater or less than the LO frequency by an amount equal to the IF frequency. That is, there are two frequencies,  $|f_{LO} \pm f_{IF}|$ , which will result in  $f_{IF}$  at the mixer output. In other words, the bands symmetrically located above and below the LO frequency are downconverted to the same center frequency. This image can be removed with the use of an image-reject filter. [8]

The local oscillator frequency can be either higher or lower than the center of the desired band. Called "high-side injection" and "low-side injection," each has trade-offs. It is usually desirable to use the latter so as to minimize the LO frequency and hence facilitate the design of the oscillator. On the other hand, if the image bands below and above the desired band exhibit different amounts of noise, then  $f_{LO}$  must be chosen so as to avoid the noisy image band.

With either high or low injection, the image is always  $2f_{IF}$  from the desired RF spectrum. In systems where adjacent channels are being used by other users, the

amount of power located at this image frequency can be quite substantial. To achieve a low loss in the channel bandwidth and high loss in the image band, one can choose  $2f_{IF}$  to be sufficiently large.

As  $2f_{IF}$  increases, so does the center of the down-converted band. The choice of IF depends on trade-offs between three parameters: the amount of image noise, the spacing between the desired band and the image, and the loss of the image-reject filter. A high  $2f_{IF}$  leads to good rejection of the image, while a low  $2f_{IF}$  allows greater suppression of nearby interferes. [15]

#### **Digital Radios & Software Radios**

The basic job of any receiver, whether it be a software radio or not, is to amplify the weak signals which it receives and demodulate these signals, all while not adding significant noise. A receiver should not allow adjacent channels or out-ofband interferers to significantly degrade the desired signal. This is known as selectivity. Finally, a receiver should be able to detect an appreciably small signal level, this is called sensitivity.

An ideal software radio is a multi-band, multimode radio with dynamic capability defined through software in all layers of the protocol stack, including the physical layer. Each band and mode is realized in a separate software-defined personality. A software radio can take on the profile of many different receiver implementations simply by reprogramming it. [10]

In the past, hardware was used to implement each of the blocks depicted in the Super-Heterodyne diagram, Figure 4. The idea behind software radios is to implement the functionality of certain blocks in software, as opposed to hardware, giving the radio the ability to perform multiple system configurations by simply reprogramming the radio. In the past, we would have implemented this solely with analog parts, which unfortunately contained components with analog tolerances. The result was a radio that performed adequately, but only in a given role. The only way to alter the radio performance was to physically change the components inside the radio.

With the advent of high-speed digital circuitry, we can convert our analog signals to digital as soon as possible in the receive chain. Once we have done this, we can perform a myriad of functions without losing any generality or information. For example, we can subject our received signal to multiple hypothesis testing, without adding extra noise. In addition, if we choose to change the way our radio behaves, we simply reprogram the digital section.

Modern software radios utilize high-speed analog-to-digital converters (ADC), and digital signal processors (DSP) to implement many of the functions illustrated in Figure 4. The ideal software radio would place the ADC at the antenna, however, this is not currently possible. Nyquist tells us that to sample a signal without losing information, we must sample at  $f_s \ge 2 \times f_h$ , where  $f_h$  is the highest frequency content of our desired signal. For example, modern cell phones operate at a carrier around 1.5 GHz, and a bandwidth of 200 kHz. Nyquist tells us that we require a sampling frequency slightly larger than  $f_s = 3$  GHz to sample this signal without loss of information. This is not practical with today's technology.

Therefore, the question arises as to where to place the ADC. Most modern systems place the ADC at the IF. Using a technique known as sub-sampling, the design engineer is able to sample the received signal at an intermediate frequency. This technique aliases the desired signal bandwidth down to a lower, more useable, frequency band. Refer to the following section for an example of how sub-sampling is used.

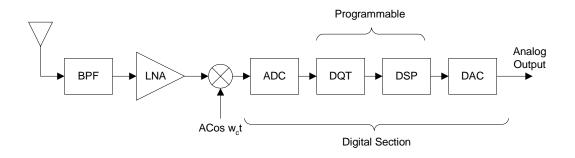

The following diagram depicts a typical software controlled radio (SWR).

13

Figure 5 – Typical Software Radio

From Figure 5, we can see the essential components in any software

radio system are the following:

- <u>A/D and D/A converters</u>. ADC's provide the link between the analog and the digital realm. DAC's provide the same, allowing digital signals to be converted back to a form which users can hear or see.

- <u>Digital Downconverters</u>. Downconverters provide the equivalent function of a mixer. Modulating parts of a digital spectrum to a different frequency band.

- <u>DSPs</u>. These processors perform the essential functions of demodulation and detection. This includes all the necessary synchronization issues for coherent detection. In addition, they can perform decoding functions. Modern DSP's perform millions of operations per second, and are easily reprogrammed.

- <u>Microcontroller</u>. The microcontroller is used to program different parts of the digital system. It initializes registers and tells the radio what functions to perform. It carries the software that controls the hardware.

Now that we have a better understanding of how a software radio may be implemented, let's look at some of the significant advantages software radios and DSPs provide. These include:

• No need for tuning. Digital filters require no tuning of their components. A digital filter will always act exactly the same as any other digital filter with the same coefficients.

- Linear phase filters. The design of FIR filters allows us to make filters with exact phase linearity. This constant phase delay helps to reduce intersymbol interference (ISI).

- Flexible bandwidth selection. If we need to select different channels from within our band, we simply reprogram the filter coefficients to achieve the desired response.

- Multiple modulation formats can be supported.

- Digital simulation is an "exact" simulation. In other words, the actual digital system should behave exactly like our digital simulations.

- System can be upgraded easily with software.

#### **Digital IF and Subsampling Receivers**

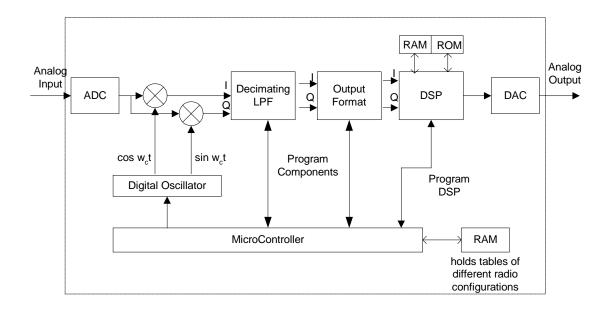

A digital IF architecture refers to the fact that we have replaced our analog components with digital ones from the IF section downward. This second set of mixing and filtering can be implemented more efficiently in the digital domain. Figure 5, from the previous page, shows a typical block diagram for a digital IF receiver. If we examine the digital section more carefully, we can get a better appreciation for what digital signal processing is necessary to complete the demodulation and detection.

The following diagram, Figure 6, shows a more detailed view of the required digital section.

Figure 6 – Detailed View of the Digital Section of a Software Radio

This is the architecture we have used in our RDRN radios. Placing the ADC at the IF section allows us to use a technique called subsampling. The idea is that a bandlimited signal with bandwidth  $\Delta f$ ,  $(f_H - f_L)$ , can be translated to a lower band if sampled at a rate equal to or greater than  $2\Delta f$ . This operation, if performed correctly, will produce replicas of the spectrum with no aliasing. The sample rate should be selected such that

$$\frac{2f_H}{k+1} < f_s < \frac{2f_L}{k}$$

where the maximum value of k is :

$$k < \frac{f_L}{f_H - f_L}$$

1

The largest value of k determines the maximum amount of sub-sampling that can be performed. [11]

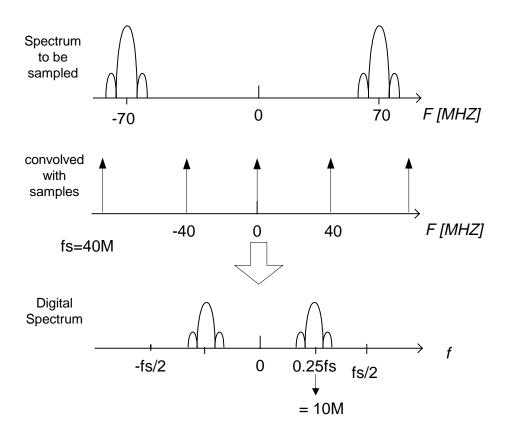

The following figure depicts an example, the one used for our radio, of sub-sampling.

Figure 7 – Sub-Sampling at the IF

I would be remiss not to point out that there are additional architectures and various other hardware techniques available to implement software radios (i.e. FPGAs). However, the RDRN radio's which we designed follow the basic superheterodyne structure and implement a software radio as depicted in the preceding section.

#### Decimation

One of the by-products of subsampling is redundant samples. For example, if we sub-sample a 70 MHz IF waveform at 40 MSPS, a copy will be placed at 10 MHz. We do not need 40 MSamples to represent this signal, some form of rate reduction is needed. Therefore, we can literally throw away the extra samples. This process of discarding unneeded samples is called "decimation." Care must be taken with digital filters that utilize decimation techniques to understand the ramifications in the frequency domain. Of primary concern is the "noise" level increase due to signals that may be aliased inside the band of interest. The potential magnitude of these signals may render significant portions of the previously thought usable bandwidth, unusable for applications that require significant (>60 dB) attenuation of undesired signals.

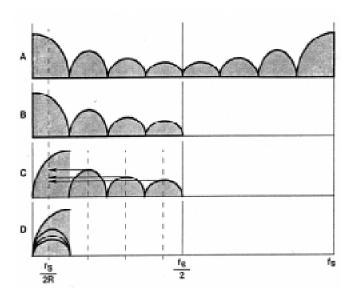

Consider a digital filter with sampling frequency  $f_s$ , whose frequency response is shown in Figure 8A, the top spectrum. At first glance the usable bandwidth would appear to be the 3 dB bandwidth of the main lobe.

Figure 8 – Aliasing Effects of Decimation

This filter is to be decimated to rate of  $\frac{1}{8}f_s$ . We concern ourselves with those elements less than  $\frac{f_s}{2}$ , as shown in Figure 8B. The decimation process will fold the various lobes of the frequency response around the new sampling folding frequency  $\frac{f_s}{2R}$ . The first lobe is folded over the dotted line and a significant portion of the first

lobe appears in the passband of the filter. Any unwanted signals in this part of the spectrum will appear in the band of interest with the greatest amplitude. The second lobe is translated down to be centered on the dashed line. The third lobe is spectrally inverted and translated to be centered on the dotted line. The fourth lobe is translated too. If more lobes were present, the process would continue to spectrally invert the

odd numbered lobes prior to translation to  $\frac{f_s}{2R}$ . This process is shown in Figure 8C.

The final diagram, Figure 8D, allows up to create an alias profile by summing the alias elements. An alias profile is used to determine what bandwidth yields the desired suppression of unwanted signals for a particular application. [6]

Due to this excessive aliasing of noise and possible interferers, the decimation process is always preceded by anti-aliasing filters. Modern DSP techniques implement the anti-aliasing filter and decimation all in one structure. In our DSP chips, these dual decimating-filter structures are the Cascade-Integrate and Comb (CIC) filters located in the Harris Digital Quadrature Tuner (DQT).

#### **Transceiver Performance Metrics**

Testing the operation of the transceiver is very important to ensure full compliance with the requirements specifications set forth. Modern wireless environments are very harsh, so the transceiver needs to be tested to be sure it will operate in such a realistic environment.

Noise figure (NF), the input 3<sup>rd</sup>-order intermodulation product (IIP3), in-band intermodulation, out-of-band intermodulation, cross modulation, and reciprocal mixing all effect receiver sensitivity and dynamic range.

The sensitivity of an RF receiver is defined as the minimum signal level that the system can detect with acceptable signal-to-noise ratio. It can be shown that the minimum detectable signal level that can be detected is (assuming conjugate matching in front end):

$$P_{in,Min} = -174 \text{ dBm} + 10 \log \text{B} + \text{NF} + \text{SNR}_{reg}$$

The first three terms represent the total integrated noise power of the system and are usually referred to as the noise floor of the receiver. It is also interesting to note that since  $P_{in,Min}$  is a function of the bandwidth, a receiver may appear very sensitive simply because it employs a narrowband channel, yet this is at the expense of a reduced information rate. [15]

Dynamic Range (DR) is generally defined as the ratio of the maximum input level that the circuit can tolerate to the minimum input level at which the circuit provides a reasonable signal quality. We base the definition of the upper end of the dynamic range on the intermodulation behavior and the lower end on the sensitivity. This is sometimes called the spurious-free-dynamic range (SFDR).

The upper end of the DR is defined as the maximum input level in a two-tone test for which the third-order IM products do not exceed the noise floor. It can be shown that the maximum input power is:

$$P_{in,Max} = \frac{2P_{IP3} + F}{3}$$

where  $F = -174 \text{ dBm} + \text{NF} + 10 \log B$  (noise floor)

From these definitions, the SFDR is the difference (in dB) between P<sub>in,max</sub> and P<sub>in,min</sub>:

$$SFDR = \frac{2P_{IIP3} + F}{3} - (F + SNR_{min})$$

$$= \frac{2(P_{IIP3} - F)}{3} - SNR_{min}$$

The SFDR represents the maximum relative level of interferers that a receiver can tolerate while producing an acceptable signal quality from a small input level.

The output of the transmitter may also contain harmonics, spurs, and thermal noise, potentially interfering with the users in other channels. Harmonics are generated in the modulator and the power amplifier (PA), while spurs arise from mixers, oscillators, and parasitic resonances and nonlinearities in the PA.

In our frequency division duplexed (FDD) system, output spurs that fall in the receive band can be particularly troublesome because the front end filter does not attenuate these signals. In addition, the front end LNA amplifies these large signals, thereby de-sensitizing the LNA. This is known as receiver desensitization.

## <u>Chapter 3</u> System Description

The RDRN radio being implemented in this research must be a flexible, modular design, capable of adaptively controlling selectable characteristics of the radios performance. In addition, it must rely heavily on software control for reprogramming and implementation of its adaptive control algorithms. In addition, it must support multiple RF front ends.

The radio must meet a number of requirements as dictated by the goals of the RDRN research. The following tables list the requirements of the transmit and receiver modules.

#### Table 3 – Transmitter Requirements

#### **Transmitter Requirements**

- Transmit within RF bands at 5.3 GHz, 2.4 GHz, and 1.2 GHz

- Frequency Agility ability to select from multiple channels within each RF band

- Average power output of +30 dBm (1W) from each antenna

- RF Bandwidth = 100 MHz

- Channel BW = 10 MHz

- Selectable QPSK or BPSK modulation

- Bit rates from 1 Mbps to 8 Mbps

- Multiple Access: FDD with TDMA/FDMA

- Transmit Power Control (2 dB steps from 5 dBm to 25 dBm)

- Transmit Power ON/OFF capability (TDMA)

- TxData received from PowerPC

- LO Spurious level  $\leq$  -28 dBm

- LO Phase Noise  $\leq$  -155 dBc/Hz at 50 MHZ offset

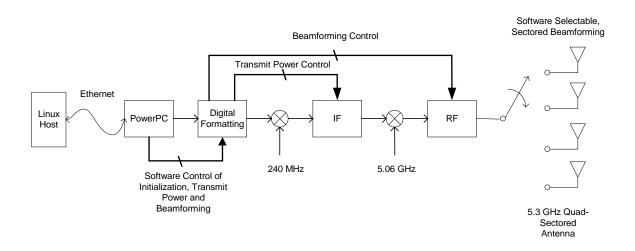

**Figure 9 – Transmitter Block Diagram**

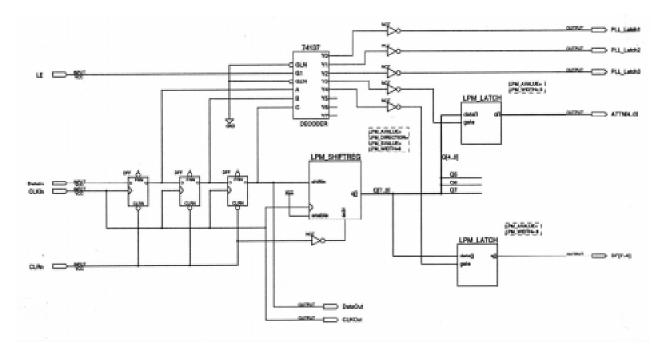

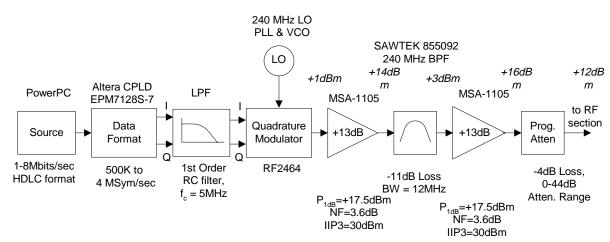

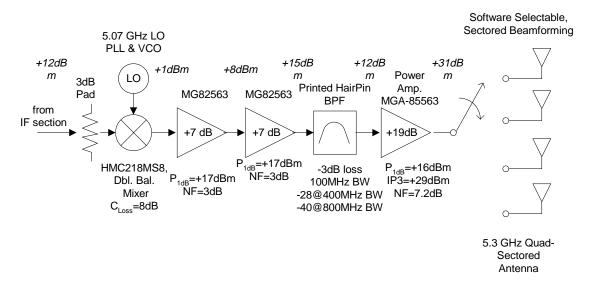

The figure above shows the complete transmitter subsystem. Data to be transmitted originates from the PowerPC. The symbol rate can be selected for 1, 2 or 4 MSymbols/sec. For QPSK this translates to a maximum 8 Mbps bit rate, while for BPSK this is 4 Mbps. There are two mixing stages, one at the IF (240 MHz), and another at the RF (5.3 GHz). The omni directional antenna is implemented with four patch antennas. This patch array is controlled by the PowerPC. The PowerPC can selectively choose which patch to radiate.

Chapter Four presents a detailed discussion of each of the sections shown above.

#### **Receiver Requirements**

- Receive within RF bands at 5.3 GHz, 2.4 GHz and 1.2 GHz

- Frequency Agility ability to select from four channels within RF band

- Full Duplex Operation

- Digital IF Architecture (subsampling)

- Demodulate QPSK or BPSK modulation

- Receiver band selectivity = 100 MHz

- Receiver channel selectivity = 10 MHz

- Bit Rates from 1 Mbps to 8 Mbps

- Dynamically configurable must be a multidimensional radio with varying software profiles (Software Radio)

- RxData passed to PowerPC

- $NF_{max} \ll 11 \text{ dB}$

- Receiver sensitivity  $\leq$  -85 dBm

- Dynamic Range  $\geq 65 \text{ dB}$

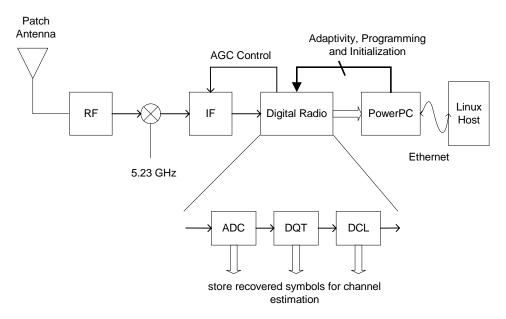

Worthy of mention above is the dynamic reconfiguration ability of the transceiver. This software control is what makes the radio such a versatile platform. Also, the digital subsampling IF places the ADC as close to the antenna as possible while not sacrificing signal quality. The following diagram, Figure 10, shows a system level view of the receive chain. A thorough discussion of each stage is left until Chapter Five.

**Figure 10 – Receiver Block Diagram**

An omni-directional antenna collects RF energy within our desired band. There is one mixing stage which uses high-side injection to downconvert the received signal to our IF, 70 MHz. High-side injection allows us to place the image band at a higher frequency than 70 MHz, in this case 5.37 GHz.. After some amplification and filtering, digital subsampling is used to alias our spectrum to 10 MHz. At this point, two DSPs are used to finish the demodulation process and recover the transmitted symbols.

A thorough discussion of each of the stages in the receive chain is presented in Chapter Five.

Based on the requirements presented in the preceding tables, we based our prototype design heavily of modularity. To incorporate each of the RF bandwidths specified, we had to separately construct multiple RF fronts ends. These front ends connect to a static IF/digital stage that remains the same for each band.

At the heart of the radio, is the PowerPC microprocessor. This processor performs all initialization and programming tasks for the radio. It carries the link

25

layer adaptation algorithms, and controls the flow of digital data to and from the radio.

#### **Multiple Access Scheme and Bandwidth Utilization**

The wireless radio spectrum is a shared resource. Therefore, users must share these resources to allow effective communication. The RDRN radio utilizes frequency-division-duplexing (FDD) on the transmit and receive paths. This facilitates the use of full-duplex communications by using separate channels for transmitting and receiving information.

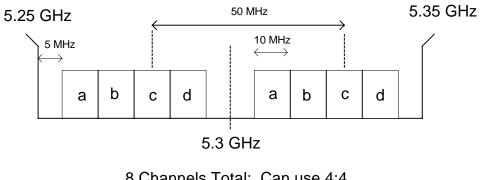

In addition, if multiple users are sharing the same channel, we have made provisions for TDMA possible. To get a better understanding of how the spectrum is used, Figure 13, below, gives a graphical representation of where the channels lie.

> RF Band = 100 MHz 1 Channel = 10 MHz

<u>8 Channels Total</u>: Can use 4:4 for full-duplex or any two channels separated by 50 MHz for peer-to-peer or simplex communications

Figure 11 – Spectrum Utilization and Channel Assignment

There are four channels, each with 10 MHz of bandwidth, within each RF band. The forward and reverse channels are separated by 50 MHz. Each RF band is 100 MHz wide. We have designed the RDRN radio to incorporate the use of modular RF stages. Each RF band (i.e., 5.3 GHz, 2.4 GHz and 1.2 GHz) uses the same spectrum assignment as the one depicted above.

The next two chapters detail how the RDRN software radio was implemented. They provide block diagrams for connectivity between components, power levels, gains and/or NF for both the transmitter and the receiver sections. Each diagram will be followed by a step-by-step explanation of each section and how it operates.

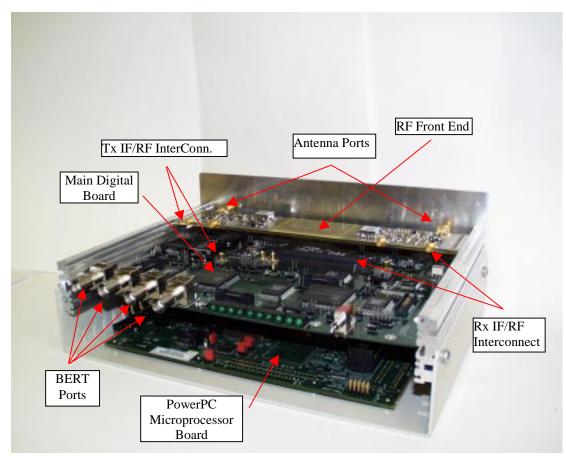

The following figure shows the major sub-sections of the radio. As shown, there are three boards: the PowerPC microprocessor (lower board), the main digital/IF radio (middle board), and the modular RF front end (top board).

Figure 12 – Completed RDRN2 Radio, including housing

#### Link Budget

The table on the following page, Table 5, shows a link budget for the RDRN2 radios. This budget is calculated for the 5.3 GHz link with a data rate of 1 Mbps using BPSK modulation. The reader may notice some cells depicted in red. This file is imported as a worksheet from Excel; these red cells depict values that must be entered by the user for a correct margin calculation.

#### Explanation of Values Calculated for Link Budget

- 1. Transmit Power from power amplifier (PA).

- 2. Circuit Losses between the PA and the antenna.

- 3. TX antenna gain referenced to an isotropic radiator at peak level (i.e., no offset)

- 4. Summation of 1-3 yields the Effective Isotropic Radiated Power (EIRP).

- 5. Free space path loss assumes an Additive White Gaussian Noise (AWGN) channel.

- 6. 2 Ray Model varies with (1/d)^4. Note: this is not used in this budget but is provided as a reference. [16]

- 7. The fade allowance is the difference between the required Eb/No ( the ratio of Energy-per-bit over the Noise Spectral Density) for a fading channel (Rayleigh/Rician) and for the AWGN case. Both extremes are calculated, but it is left to user to pick the fade margin.

- 8. Allowances are made for polarization losses, weather fades, or any number of other losses.

- 9. Total path loss is the amount of signal level lost due to propagation from the transmitter to the receiver. It is the sum of 5, 7 and 8.

- 10. Received Isotropic power refers to the power that would be received if the receiving antenna were isotropic.

- 11. RX antenna gain referenced to an isotropic radiator at peak level.

- Edge of coverage loss is due to the off-axis antenna gain (compared to peak gain) and to the increased range for users at the extreme edge of communication coverage (a nominal 2 dB loss is shown here).

- 13. The input power to the receiver, tallied from 10, 11 and 12.

- 14. Computes the system equivalent temperature from the system noise figure and background antenna temperature.

- 15. Figure of merit for a receiver, the G/T is formed from 11 minus 14.

- 16. Form the noise spectral density by multiplying boltzmann's constant by 14.

- 17. Form the received signal to noise spectral density by subtracting 16 from 13.

- 18. The data rate listed in dB-bps.

- 19. Eb/No = (1/R)(Pr/No). Form this by subtracting 18 from 17.

- 20. We can achieve the same BER with a decreased Eb/No if we employ coding. None is used here.

- 21. Accounts for the difference between theoretically predicted detection performance, and the performance of the actual detector.

- 22. The required Eb/No is derived from the desired BER and the modulation format.

- 23. The difference between the required Eb/No and the received Eb/No gives us the final margin.

# Link Budget for RDRN2 Radios

| Date        | : April '99                            |                      | ttc.ukans.edu            |

|-------------|----------------------------------------|----------------------|--------------------------|

| fc =        | 5.30 GHz ** ite                        | ems in "yellow" nee  | d                        |

| k =         | -228.6 dBW/Hz to                       | be filled in by user |                          |

|             |                                        |                      |                          |

| 1.          | Transmit Power 1 W                     | ,                    | 0 dBW                    |

| 2.          | Transmitter Ckt Loss                   |                      | -1 dB                    |

| 3.          | Transmitter Ant. Gain (peak dBi)       |                      | 5.0 dBi                  |

| 4.          | Transmit EIRP                          |                      | 4.0 dBW                  |

| 5.          | Free Space Path Loss                   |                      | 120.6 dB                 |

|             | Distance [miles]                       | 3                    |                          |

| 6.          | 2Ray Model Path Loss                   | -135.3 dB            |                          |

|             | ht [m] = 2                             |                      |                          |

|             | hr [m] = 2                             |                      |                          |

|             | Path Diff. [m] 0.0017                  |                      |                          |

| 7.          | Fade Allowance                         |                      | -4.0 dB                  |