### 4.5 Biasing in BJT Amplifier Circuits

#### Reading Assignment: 280-286

Now let's examine how we DC bias MOSFETs amplifiers!

If we don't bias properly, distortion can result!

EXAMPLE: MOSFET AMPLIFIER DISTORTION

There is a classic bias circuit for **MOSFET amplifiers**; let's see what it is!

HO: MOSFET BIASING USING A SINGLE POWER SUPPLY

Let's do an example DC bias design.

EXAMPLE: BIASING OF DISCRETE MOSFET AMPLIFIERS

We can also use a DC current source to bias the Amplifier.

Q: Yes, but just how do we construct a current source?

A: HO: THE MOSFET CURRENT MIRROR

HO: CURRENT STEERING CIRCUITS

#### HO: MOSFET BIASING USING CURRENT MIRRORS

#### EXAMPLE: MOSFET BIASING USING CURRENT MIRRORS

# <u>Example: MOSFET</u> <u>Amplifier Distortion</u>

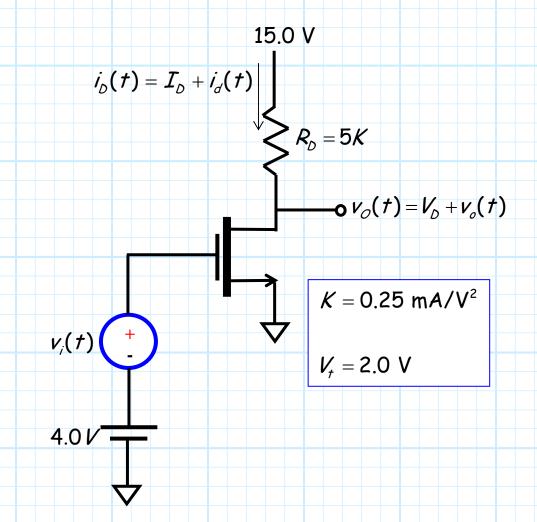

Recall this circuit from a **previous** handout:

We found that the small-signal voltage gain is:

$$\mathcal{A}_o = \frac{v_o(t)}{v_i(t)} = -5.0$$

Say the **input** voltage to this amplifier is:

$v_i(t) = V_i \cos \omega t$

**Q:** What is the **largest** value that V<sub>i</sub> can take without producing a **distorted** output?

A: Well, we know that the small-signal output is:

$$v_o(t) = A_{v_o} v_i(t)$$

$$= -5.0 V_i \cos \omega t$$

BUT, this is not the output voltage!

The **total** output voltage is the **sum** of the **small-signal** output voltage and the **DC** output voltage!

Note for this example, the **DC output** voltage is the **DC drain** voltage, and we recall we determined in an earlier handout that its value is:

$$V_{\mathcal{O}} = V_{\mathcal{D}} = 10 \text{ V}$$

Thus, the total output voltage is :

$$v_{O}(t) = V_{D} + v_{o}(t)$$

= 10.0 - 5.0  $V_{i} \cos \omega t$

3/9

Let's break the problem down into two separate problems: 1) If total output voltage  $v_{\mathcal{O}}(t)$  becomes too small, the MOSFET will enter the triode mode. 2) If total output voltage  $v_{\mathcal{O}}(t)$  becomes too large, the MOSFET will enter cutoff. We'll first consider problem 1. For a MOSFET to remain in saturation,  $v_{D,S}(t)$  must remain greater than the excess gate voltage  $(V_{GS} - V_{T})$  for all time *t*.  $V_{DS}(t) > V_{GS} - V_{t}$ Since the source terminal of the MOSFET in this circuit is connected to ground, we know that  $V_{s} = 0 V$ . Therefore:  $v_{\mathcal{D},\mathcal{S}}(t) = v_{\mathcal{D}}(t) = v_{\mathcal{O}}(t)$  and  $V_{GS} = V_{G}$ And so the MOSFET will remain in saturation only if the total output voltage remains larger than  $V_{GS} - V_t = V_G - V_t!$  $V_{\mathcal{O}}(t) > V_{\mathcal{C}} - V_{t}$

Thus, we conclude for this amplifier that the output "floor" is:

$L_{-} = V_{G} - V_{t}$

And since  $V_{G} = 4.0 V$  and  $V_{f} = 2.0 V$ , we find:

$L_{-} = V_{G} - V_{t} = 4 - 2 = 2.0 V$

Thus, to remain in saturation, the **total** output voltage must remain larger than the "floor" voltage  $L_{1}$  for all time t:

$$V_{O}(t) > L_{-} = 2.0 V$$

Since this total voltage is:

$$v_{O}(t) = 10.0 - 5.0 V_{i} \cos \omega t$$

we can determine the **maximum** value of small-signal **input** magnitude V<sub>i</sub>:

$$10.0 - 5.0 V_i \cos \omega t > 2.0$$

$$\Rightarrow$$

8.0 > 5.0 V<sub>i</sub> cos*wt*

$$\Rightarrow$$

V<sub>i</sub> coswt < 1.6

Since coswt can be as large as 1.0, we find that the **magnitude** of the **input** voltage can be **no larger** than 1.6 V, i.e.,

$$V_{i} < 1.6 V$$

If the **input** magnitude exceeds this value, the MOSFET will (momentarily) leave the saturation region and enter the dreaded **triode** mode!

Now let's consider problem 2

For the MOSFET to remain in saturation, the **drain** current must be **greater** than zero (i.e.,  $i_D > 0$ ). Otherwise, the MOSFET will enter **cutoff** mode.

Applying Ohm's Law to the drain resistor, we find the drain current is:

$i_{D} = \frac{V_{DD} - v_{O}}{R_{C}} = \frac{15 - v_{O}}{5}$

it is evident that drain current is **positive** only if  $v_{O}$  < 15 V.

In other words, the **upper** limit (i.e., the "ceiling") on the **total** output voltage is:

$$L_{\!_+} = V_{\!_{DD}} = 15.0 V$$

Since:

$$v_{\mathcal{O}}(t) = 10.0 - 5.0 V_i \cos \omega t$$

we can conclude that in order for the MOSFET to remain in saturation mode:

$10 - 5.0 V_i \cos \omega t > 15.0$

Therefore, we find:

$$V_{s}\cos \omega t > \frac{-5.0}{5.0} = -1.0$$

Since  $\cos \omega t \ge -1$ , the above equation means that the input signal magnitude  $V_i$  can be no larger than:

$$V_i < 1.0 \text{ V}$$

If the input magnitude **exceeds** 1.0 V, the MOSFET will (momentarily) leave the saturation and enter the **cutoff** region!

#### In summary:

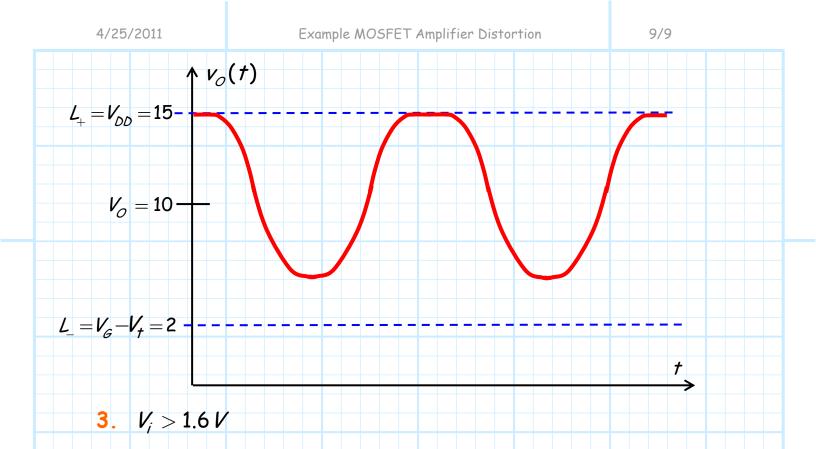

**1)** If  $V_i > 1.6$  V, the MOSFET will at times enter **triode**, and **distortion** will occur!

**2)** If  $V_i > 1.0$  V, the MOSFET will at times enter **cutoff**, and **even more** distortion will occur!

*†*

To demonstrate this, let's consider **three** examples:

#### **1**. $V_i < 1.0 V$

The output signal in this case remains between  $V_{DD} = 15.0$  and  $V_G - V_f = 2.0$  V for all time t. Therefore, the output signal is not distorted.

$\uparrow V_o(t)$

$$V_{\mathcal{O}} = 10$$

2. 1.6 V >

$$V_i$$

> 1.0 V

The output signal in this case remains greater than  $L_{-} = V_{G} - V_{f} = 2$ for all time *t*. However, the small-signal output is now large enough so that the total output voltage at times tries to **exceed**  $L_{+} = V_{DD} = 15$ . For these times, the MOSFET will enter **cutoff**, and the output signal will be **distorted**.

In this case, the small-signal input signal is sufficiently large so that the total output will attempt to exceed **both** limits (i.e.,  $V_{DD} = 15.0$  V and  $V_G - V_f = 2.0$  V). Therefore, there are periods of time when the MOSFE will be in **cutoff**, and periods when the MOSFET will be in **saturation**.

$$\lambda_{+} = V_{DD} = 15$$

†

$$V_{c} = 10 -$$

$$L_{-}=V_{G}-V_{t}=2$$

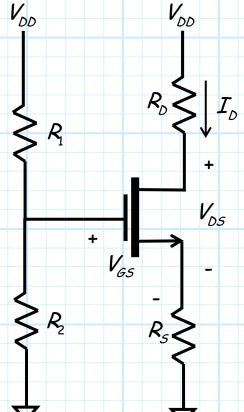

# <u>MOSFET Biasing using a</u> <u>Single Power Supply</u>

The general form of a **single**-supply MOSFET amplifier biasing circuit is:

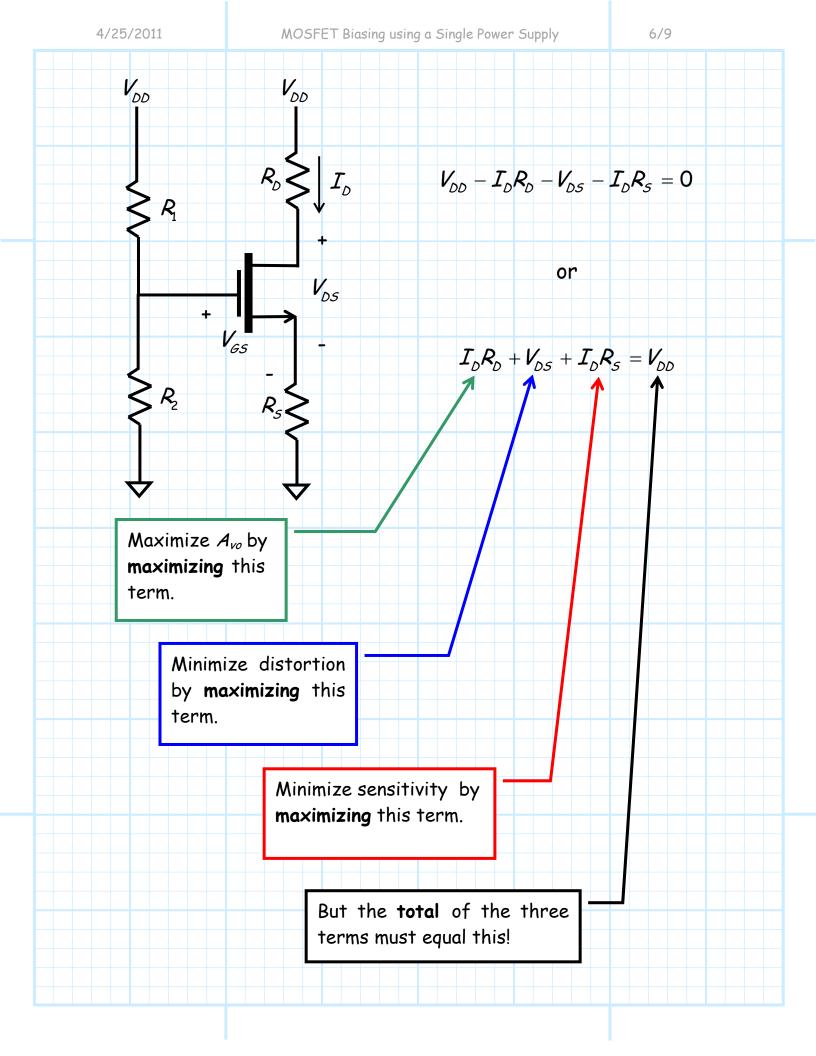

Just like BJT biasing, we typically attempt to satisfy three main bias design goals:

#### 1) Maximize Gain

Typically, the small-signal voltage gain of a MOSFET amplifier will be proportional to transconductance  $g_m$ :

### $A_{vo} \propto g_m$

Thus, to maximize the amplifier voltage gain, we must **maximize** the MOSFET transconductance.

#### Q: What does this have to do with D.C. biasing?

A: Recall that the transconductance depends on the DC excess gate voltage:

$$g_m = 2 K \left( V_{GS} - V_{t} \right)$$

Another way to consider transconductance is to express it in terms of DC drain current  $I_{D}$ . Recall this DC current is related to the DC excess gate voltage (in satureation!) as:

$$I_{D} = K \left( V_{GS} - V_{t} \right)^{2} \implies \left( V_{GS} - V_{t} \right) = \sqrt{\frac{I_{D}}{K}}$$

And so transconductance can be alternatively expressed as:

$$g_m = 2 K (V_{GS} - V_t) = 2 K \sqrt{\frac{I_D}{K}} = 2 \sqrt{K I_D}$$

Therefore, the amplifier voltage gain is typically **proportional** to the square-root of the DC drain current:

$$A_{vo} \propto \sqrt{I_D}$$

#### To maximize $A_{\!\scriptscriptstyle O}$ , maximize $I_{\!\scriptscriptstyle D}$

#### 2) Maximize Voltage Swing

Recall that if the DC drain voltage  $V_D$  is biased too close to  $V_{DD}$ , then even a small small-signal drain voltage  $v_d(t)$  can result in a **total** drain voltage that is too **large**, i.e.:

$$v_{D}(t) = V_{D} + v_{d}(t) \geq V_{DD}$$

In other words, the MOSFET enters **cutoff**, and the result is a **distorted** signal!

To avoid this (to allow  $v_d(t)$  to be as large as possible without MOSFET entering cutoff), we need to bias our MOSFET such that the DC drain voltage  $V_p$  is as **small** as possible.

Note that the drain voltage is:

$$V_D = V_{DD} - R_D I_D$$

Therefore  $V_D$  is minimized by designing the bias circuit such that the DC drain current  $I_D$  is as large as possible.

However, we must **also** consider the signal distortion that occurs when the MOSFET enters **triod**. This of course is avoided if the total voltage drain-to-source remains greater than the excess gate voltage, i.e.:

$$\boldsymbol{v}_{DS}(t) = \boldsymbol{V}_{DS} + \boldsymbol{v}_{dS}(t) > \left(\boldsymbol{V}_{GS} - \boldsymbol{V}_{t}\right)$$

Thus, to avoid the MOSFET triode mode—and the resulting signal distortion—we need to bias our MOSFET such that the DC voltage  $V_{DS}$  is as **large** as possible.

To minimize signal distortion, maximize  $V_{DS}$

#### 3) Minimize Sensitivity to changes in $K_{,V_{+}}$

We find that MOSFETs are sensitive to temperature—specifically, the value of K is a function of temperature.

Likewise, the values of K and threshold voltage  $V_{r}$  are not particularly constant with regard to the manufacturing process.

Both of these facts lead to the requirement that our bias design be **insensitive** to the values of K and  $V_{f}$ . Specifically, we want to design the bias network such that the DC bias current does **not** change values when K and/or  $V_{f}$  does.

**Mathematically**, we can express this requirement as minimizing the value:

Similar to the BJT, we find that these derivatives are minimized by maximizing the value of **source resistor**  $R_s$ .

To minimize  $d I_{\rm D}/dK$  , maximize  $R_{\rm S}$

So, let's **recap** what we have learned about designing our bias network:

- **1**. Make  $I_D$  as large as possible.

- 2. Make  $V_{DS}$  as large as possible.

- **3**. Make  $R_s$  as large as possible.

Again analogous to BJT biasing, we find that these three goals are conflicting, as they are constrained by the KVL equation of the bias circuit:

(1)

Resolving this conflict is a subject choice of the amplifier designer. However, here is a "rule-of-thumb" procedure.

However, verify that these results satisfy your design requirements (or the requirements assigned to you by your boss and/or professor!).

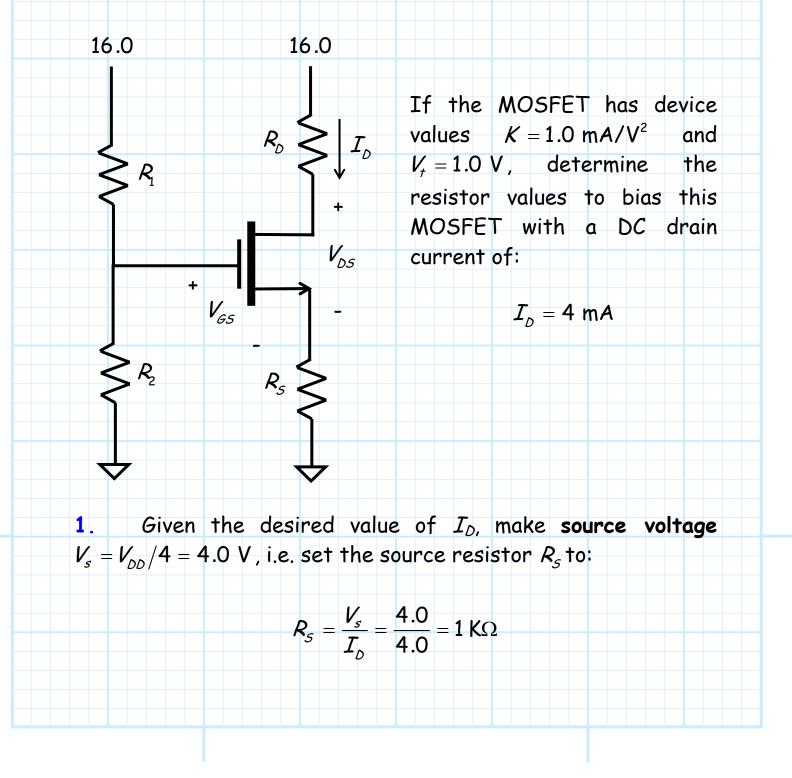

1. Given the **desired value** of  $I_D$ , make source voltage  $V_s = V_{DD}/4$ , i.e. set the source resistor  $R_s$  to:

$$\mathcal{R}_{S} = \frac{V_{S}}{I_{D}} = \frac{V_{DD}}{4I_{D}}$$

This value reduces the sensitivity  $d I_D/dK$  !

2. Now determine the required value of  $V_{GS}$ . Since  $I_D = K(V_{GS} - V_t)^2$ , we find that  $V_{GS}$  should be:

$$V_{GS} = \sqrt{\frac{I_{D}}{K} + V_{t}}$$

3. Set the required value of gate voltage  $V_{G}$ .

Note that:

$$V_G = V_{GS} + V_S$$

Thus, we can **add** the results of the previous **two** steps to find the required value of the gate voltage  $V_{c}$ . To set the gate voltage to this value, we must select the proper values of **resistors**  $R_1$  and  $R_2$ .

Since the gate current is **zero**  $(i_{\beta} = 0)$ , we find from voltage division that:

$$V_{G} = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right) = \frac{V_{DD}}{\left( \frac{R_1}{R_2} \right) + 1}$$

Note this equation determines the **ratio** of resistors  $R_1$  and  $R_2$ , but not the resistors themselves.

We need a **second** equation to explicitly determine the resistors values—the **sum** of the two resistances, for example.

We find that making the resistances  $R_1$  and  $R_2$  as **large** as possible is **very desirable**! This will typically maximize the amplifier input resistance, as well as result in minimum power dissipation.

As a result, we make the resistors as **large a practicable**. For **example**:

$$R_1 + R_2 = 250 \text{ K}$$

(3)

(2)

**4**. Set the required value of DC drain voltage  $V_{D}$ .

Recall that:

**a)** we require  $V_D \ll V_{DD} = L_{+}$  to avoid **cutoff** mode.

(4)

**b)** and, we require that  $V_D \gg V_G - V_t = L$  to avoid **triode** mode.

**Solution:** set the drain voltage  $V_D$  to a value half-way between  $V_{DD}$  and  $V_G - V_t$ !

In other words, set the DC drain voltage to be:

$$V_{D} = \frac{V_{DD} + (V_{G} - V_{t})}{2}$$

To achieve this, we must select the drain resistor  $R_{p}$  so that:

$$\boldsymbol{R}_{D} = \frac{\boldsymbol{V}_{DD} - \boldsymbol{V}_{D}}{\boldsymbol{I}_{D}} = \frac{\boldsymbol{V}_{DD} - (\boldsymbol{V}_{G} - \boldsymbol{V}_{T})}{2\boldsymbol{I}_{D}}$$

Thus, use equations (1), (2), (3), and (4) to determine the **standard** DC bias design (i.e.,  $R_1$ ,  $R_2$ ,  $R_s$ , and  $R_D$ ) for MOSFET amplifiers.

If I were you, I'd make sure I understood this material well enough that I could also bias a **non-standard** MOSFET amplifier problem.

It's not enough to simply know how, you must also know **why**!

# <u>Example: Biasing of</u> <u>Discrete MOSFET</u> <u>Amplifiers</u>

2. Now determine the required value of  $V_{GS}$ . Since  $I_{D} = K(V_{GS} - V_{t})^{2}$ , we find that  $V_{GS}$  should be:  $V_{GS} = \sqrt{\frac{I_D}{K}} + V_{t}$  $=\sqrt{\frac{4.0}{1.0}}+1.0$ = 3.0 V 3. Set the required value of gate voltage  $V_{G}$ .  $V_{G} = V_{GS} + V_{S}$ = 3.0 + 4.0= 7.0 V Since the gate current is **zero**  $(i_{\mathcal{G}} = 0)$ , we find from voltage division that:  $V_{G} = \frac{V_{DD}}{\left(\frac{R_{I}}{R_{I}}\right) + 1}$ Therefore:  $\frac{R_1}{R_2} = \frac{V_{DD}}{V_c} - 1$  $=\frac{16.0}{7.0}-1$  $=\frac{9}{7}$

We need a **second** equation to explicitly determine the resistors values—the **sum** of the two resistances, for example.

We make the resistors as large a practicable. For **example**:

$$R_1 + R_2 = 240 \text{ K}$$

Therefore:

$$\frac{9}{7}R_2 + R_2 = 240$$

$$\frac{16}{7}R_2 = 240$$

and thus:

$$R_1 = 135 \text{ K}\Omega$$

and  $R_2 = 105 \text{ K}\Omega$

4. Set the required value of DC drain voltage  $V_{\rho}$ .

Set the drain voltage  $V_D$  to a value half-way between  $V_{DD}$  and  $V_G - V_f!$

In other words, set the DC drain voltage to be:

$$V_{D} = \frac{V_{DD} + (V_{G} - V_{f})}{2}$$

$$= \frac{16 + (7.0 - 1.0)}{2}$$

$$= 11.0 \text{ V}$$

## <u>The MOSFET</u> <u>Current Mirror</u>

$I_{D}$

$\sum_{R}$

Consider the following MOSFET circuit: VDD

Note  $V_D = V_G$ , therefore:

$$V_{DS} = V_{GS}$$

and thus:

$$V_{DS} > V_{GS} - V_{t}$$

So, if  $V_{GS} > V_{t}$ , then the MOSFET is in saturation!

We know that for a MOSFET in saturation, the drain current is equal to:

$$\mathcal{I}_{D} = \mathcal{K} \left( \mathcal{V}_{GS} - \mathcal{V}_{t} \right)^{2}$$

Say we want this current  $I_D$  to be a specific value—call it  $I_{ref}$ .

Since  $V_s = 0$ , we find that from the above equation, the drain voltage must be:

$$V_{D} = \sqrt{rac{I_{ref}}{K} + V_{r}}$$

#### Likewise, from KVL we find that:

$$I_{ref} = \frac{V_{DD} - V_{D}}{R}$$

And thus the **resistor** value to achieve the desired drain current  $I_{ref}$  is:

$R = \frac{V_{DD} - V_{D}}{I_{ref}}$

$$V_{\mathcal{D}} = \sqrt{rac{I_{ref}}{K}} + V_{t}$$

#### Q: Why are we doing this?

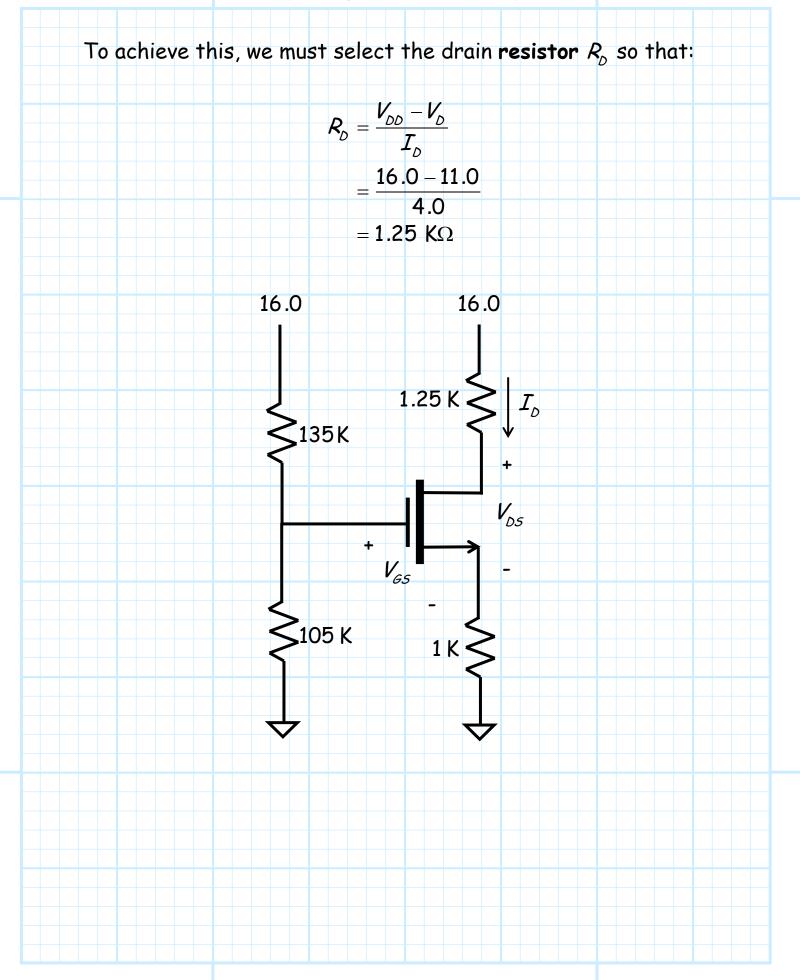

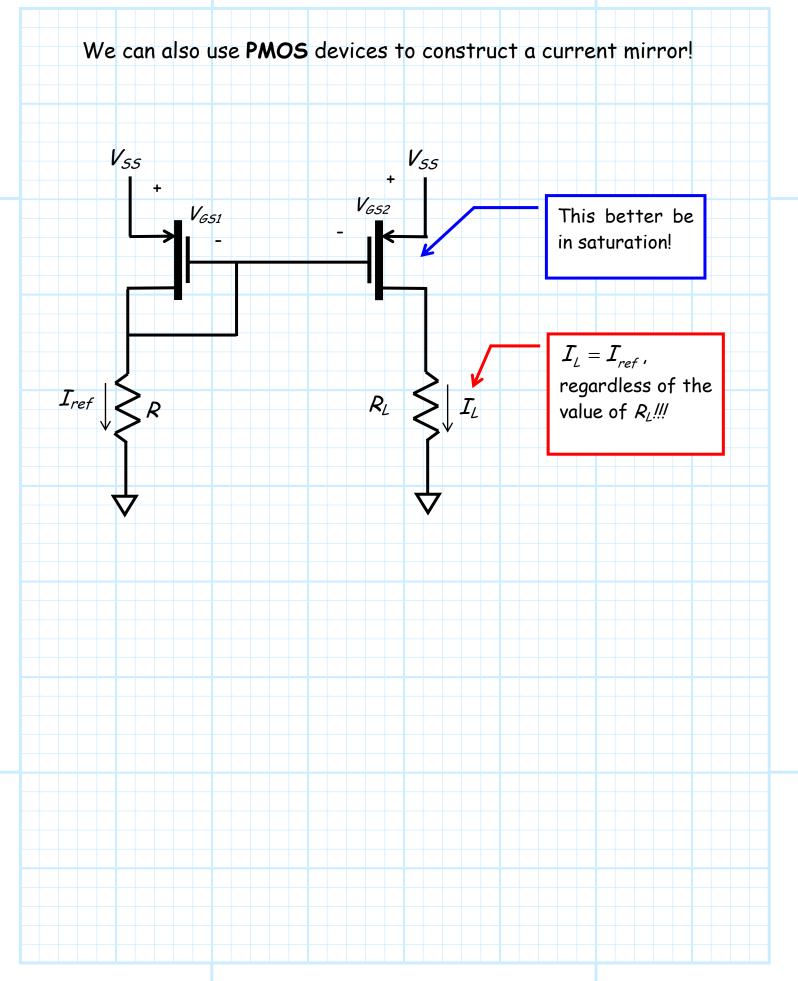

A: Say we now add another component to the circuit, with a second MOSFET that is **identical** to the first :

**Q:** So what is current  $I_L$ ?

A: Note that the gate voltage of each MOSFET is the same (i.e.,  $V_{G51} = V_{G52}$ ), and if the MOSFETS are the same (i.e.,  $K_1 = K_2$ ,  $V_{r1} = V_{r2}$ ), and if the second MOSFET is likewise in saturation, its drain current  $I_L$  is:

$$I_{L} = K_{2} \left( V_{G52} - V_{t2} \right)^{2} \\

= K_{1} \left( V_{G51} - V_{t1} \right)^{2} = I_{rep}$$

Therefore, the drain current of the **second** MOSFET is **equal** to the current of the **first**!

$$I_{ref} = I_L$$

**Q:** Wait a minute! You mean to say that the current through the resistor  $R_L$  is **independent** of the value of resistor  $R_L$ ?

A: Absolutely! As long as the second MOSFET is in saturation, the current through  $R_L$  is equal to  $I_{ref}$ —period.

The current through  $R_{L}$  is independent on the value of  $R_{L}$ (provided that the MOSFET remains in saturation). Think about what this means—this device is a **current source**!

Remember, the second MOSFET **must** be in saturation for the current through  $R_L$  to be a constant value  $I_{ref}$ . As a result, we find that:

$$V_{D52} > V_{G52} - V_{t2}$$

or for this example, since  $V_s = 0$ :

$$V_{D2} > V_{G2} - V_{t2}$$

Since  $V_{D2} = V_{DD} - R_L I_{ref}$ , we find that in order for the MOSFET to be in saturation:

$$V_{DD} - R_L I_{ref} > V_{G2} - V_{t2} = V_{G1} - V_{t1}$$

Or, sated another way, we find that the load resistor  $R_L$  can be **no larger** than:

$R_L < \frac{V_{DD} - V_{G1} + V_{f1}}{I_{ref}}$

Where we know that:

$$V_{G1} = V_{DD} - R I_{ref}$$

and thus we can alternatively write the above equation as:

$$R_L < R + rac{V_{r1}}{I_{ref}}$$

If the load resistor becomes larger than  $R + V_{t1}/I_{ref}$ , the voltage  $V_{DS2}$  will drop below the excess gate voltage  $V_{GS2} - V_{t2}$ , and thus the second MOSFET will enter the triode region. As a result, the drain current will not equal  $I_{ref}$  —the current source will stop working!

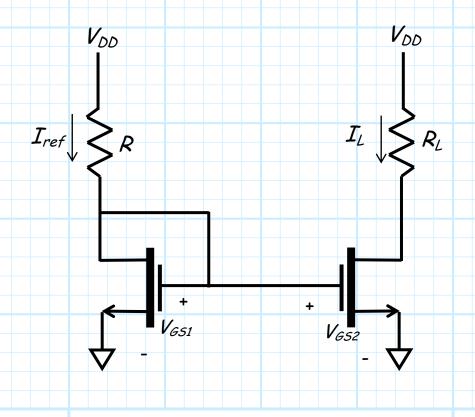

Although the circuit presented here is sometimes referred to as a current sink, understand that the circuit is clearly a way of designing a current source.

VDD

RŚ

Iref

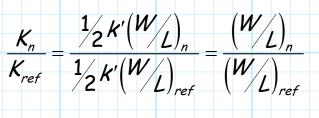

### **Current Steering Circuits**

A current mirror may consist of **many** MOSFET current sources!

VDD

$Q_2$

$R_{L1} \underbrace{}_{L1} = I_{ref} \qquad R_{L2} \underbrace{}_{L2} = I_{ref} \qquad R_{L3} \underbrace{}_{L3} = I_{ref}$

VDD

This circuit is particularly useful in integrated circuit design, where **one** resistor *R* is used to make **multiple** current sources.

**Q:** What if we want to make the sources have **different** current values? Do we need to make **additional** current mirrors?

#### **A:** NO!!

Recall that the current mirror simply ensures that the gate to source voltages of **each** transistor is **equal** to the gate to source voltage of the **reference**:

VDD

$$V_{GS}^{ref} = V_{GS1} = V_{GS2} = V_{GS3} = \cdots$$

Therefore, **if** each transistor is identical (i.e.,  $K_{ref} = K_1 = \cdots$ , and  $V_t^{ref} = V_{t1} = V_{t2} = \cdots$ ) then:

$$I_{ref} = K_{ref} \left( V_{GS}^{ref} - V_t^{ref} \right)^2$$

$$= K_n \left( V_{GSn} - V_{tn} \right)^2 = I_{Dn}$$

In other words, if each transistor  $Q_n$  is identical to  $Q_{ref}$ , then each current  $I_{Dn}$  will equal reference current  $I_{ref}$ .

**But**, consider what happens if the MOSFETS are not identical. Specifically, consider the case where  $K_n \neq K_{ref}$  (but  $V_{tn} = V_t^{ref}$ ).

Remember, we know that  $V_{GSn} = V_{GS}^{ref}$  still, even when  $K_n \neq K_{ref}$ . Thus, the drain current  $I_{Dn}$  will now be:

$$I_{Dn} = K_n \left( V_{GSn} - V_{tn} \right)^2$$

$$= K_n \left( V_{GS}^{ref} - V_t^{ref} \right)^2$$

$$= K_n \left( \frac{I_{ref}}{K_{ref}} \right)$$

$$= \left( \frac{K_n}{K_{ref}} \right) I_{ref}$$

The drain current is a scaled value of  $I_{ref}$ !

3/3

For example, if  $K_1$  is twice that of  $K_{ref}$  (i.e.,  $K_1 = 2K_{ref}$ ), then  $I_{D1}$ will be twice as large as  $I_{ref}$  (i.e.,  $I_1 = 2I_{ref}$ ).

From the standpoint of integrated circuit design, we can change the value of K by modifying the MOSFET channel width-tolength ratio (W/L) for each transistor.

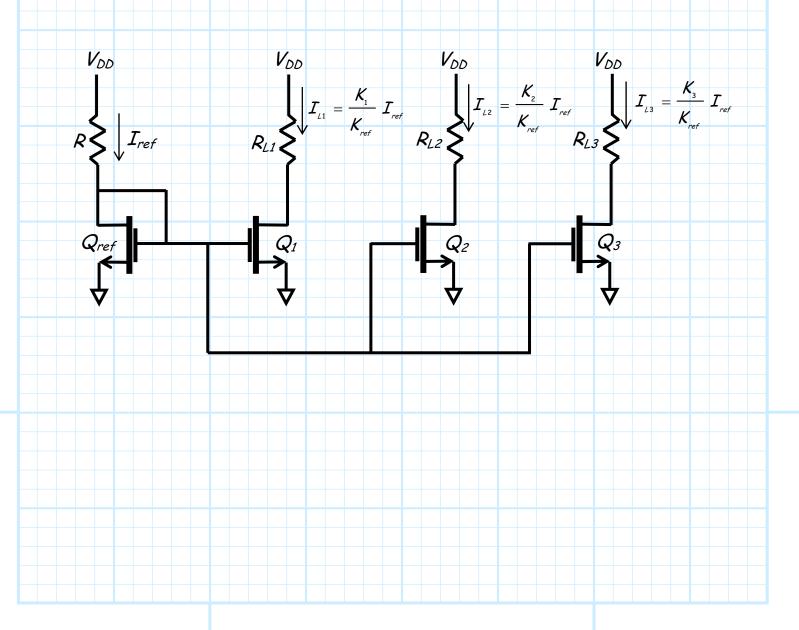

## <u>MOSFET Biasing using a</u> <u>Current Mirror</u>

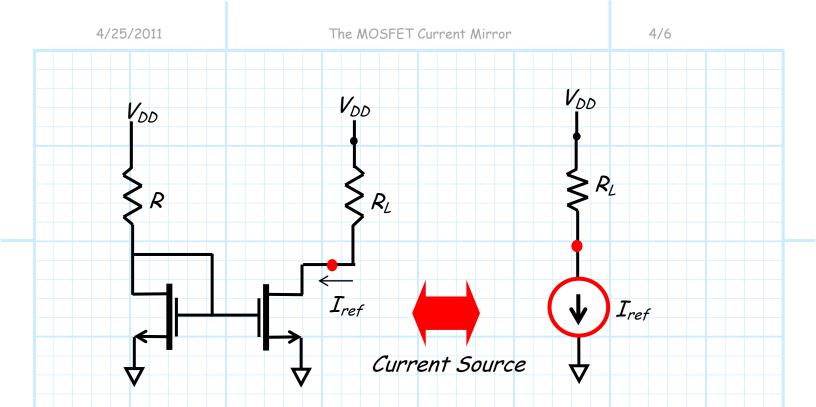

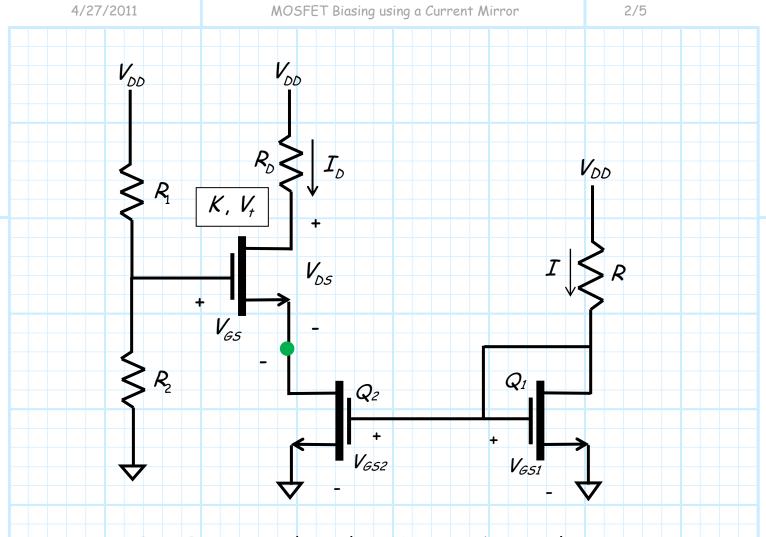

Just as with BJT amplifiers, we can likewise bias a MOSFET amplifier using a current source:

It is evident that the DC drain current  $I_D$ , is equal to the current source I, **regardless** of the MOSFET values K or  $V_{\tau}!$

Thus, this bias design maximizes drain current **stability**!

We now know how to implement this bias design with MOSFETs—we use the **current mirror** to construct the current source!

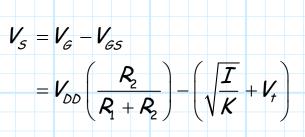

Since  $I_D = I$ , it is evident that  $V_{GS}$  must be equal to:

$$V_{GS} = \sqrt{\frac{I}{K} + V_{t}}$$

and since the DC gate voltage is:

$$V_{\mathcal{G}} = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$$

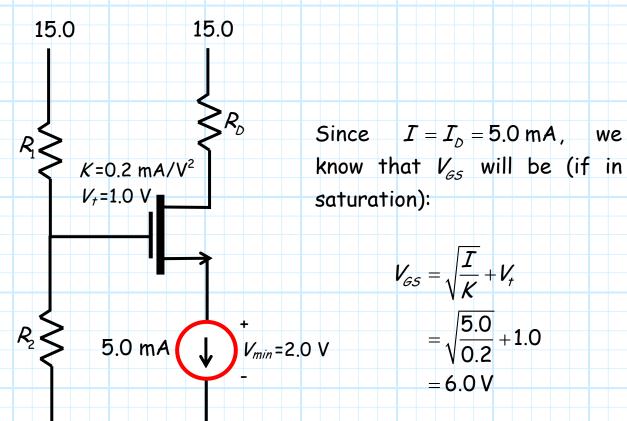

It is evident that the DC source voltage  $V_{S}$  is thus:

Since we are biasing with a current source, we do **not** need to worry about drain current **stability**—the current source will determine the DC drain current for **all** conditions (i.e.,  $I_D = I$ ).

We might conclude therefore, that we should make DC source voltage  $V_S$  as small as possible. After all, this would allow us to maximize the output voltage swing (i.e., maximize  $I_D R_D$  and  $V_{DS}$ ).

Note however, that the source voltage  $V_s$  of the MOSFET is numerically equal to the drain voltage  $V_{D2}$  (and thus  $V_{D32}$ ) of the second MOSFET of the current mirror.

#### Q: So what?!

A: The voltage  $V_{DS2} = V_S$  must be greater than:

$$V_{GS2} - V_{t2} = V_{GS1} - V_{t1} \\ = (V_{DD} - I_{ref}R) - V_{t1}$$

in order for the second MOSFET to remain in saturation.

There is a **minimum voltage** across the current source in order for the current source to properly operate!

Thus, to maximize output swing, we **might** wish to set:

$$V_{\mathcal{S}} = V_{\mathcal{GS}1} - V_{t1}$$

(although to be practical, we should make  $V_s$  slightly greater than this to allow for some design margin).

Q: How do we "set" the DC source voltage V<sub>s</sub> ??

A: By setting the DC gate voltage  $V_G$ !!

Recall that the DC voltage  $V_{GS}$  is determined by the DC current source value I:

$$V_{GS} = \sqrt{\frac{I}{K}} + V_{SS}$$

and the DC gate voltage is determined by the **two** resistors  $R_1$  and  $R_2$ :

$$V_{G} = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$$

Thus, we should **select** these resistors such that:

$$V_{G} = V_{GS} + V_{S}$$

$$= \left(\sqrt{\frac{I}{K}} + V_{t}\right) + \left(V_{GS1} - V_{t1}\right)$$

**Q:** So what should the value of resistor  $R_{D}$  be?

A: Recall that we should set the DC drain voltage  $V_D$ :

a) much less than  $V_{DD}$  to avoid cutoff.

b) much greater than  $V_{\mathcal{G}} - V_t$  to avoid triode.

Thus, we **compromise** by setting the DC drain voltage to a point **halfway** in between!

$$V_{\mathcal{D}} = \frac{V_{\mathcal{D}\mathcal{D}} + (V_{\mathcal{G}} - V_{\tau})}{2}$$

To achieve this, we must select the drain resistor  $R_{D}$  so that:

$$\mathbf{R}_{D} = \frac{\mathbf{V}_{DD} - \mathbf{V}_{D}}{\mathbf{I}_{D}} = \frac{\mathbf{V}_{DD} - (\mathbf{V}_{G} - \mathbf{V}_{t})}{\mathbf{I}_{D}}$$

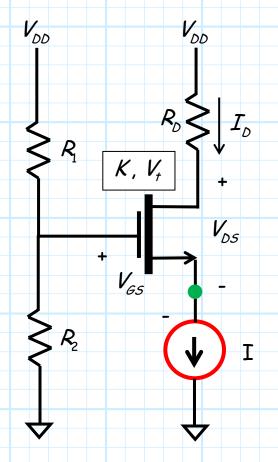

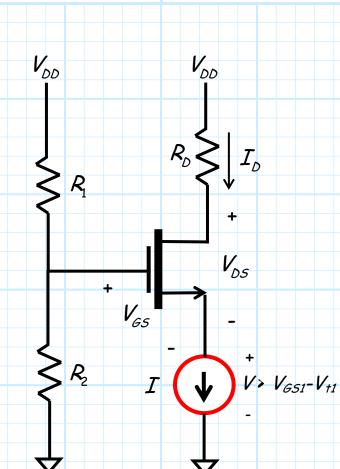

### <u>Example: MOSFET Biasing</u> <u>using a Current Mirror</u>

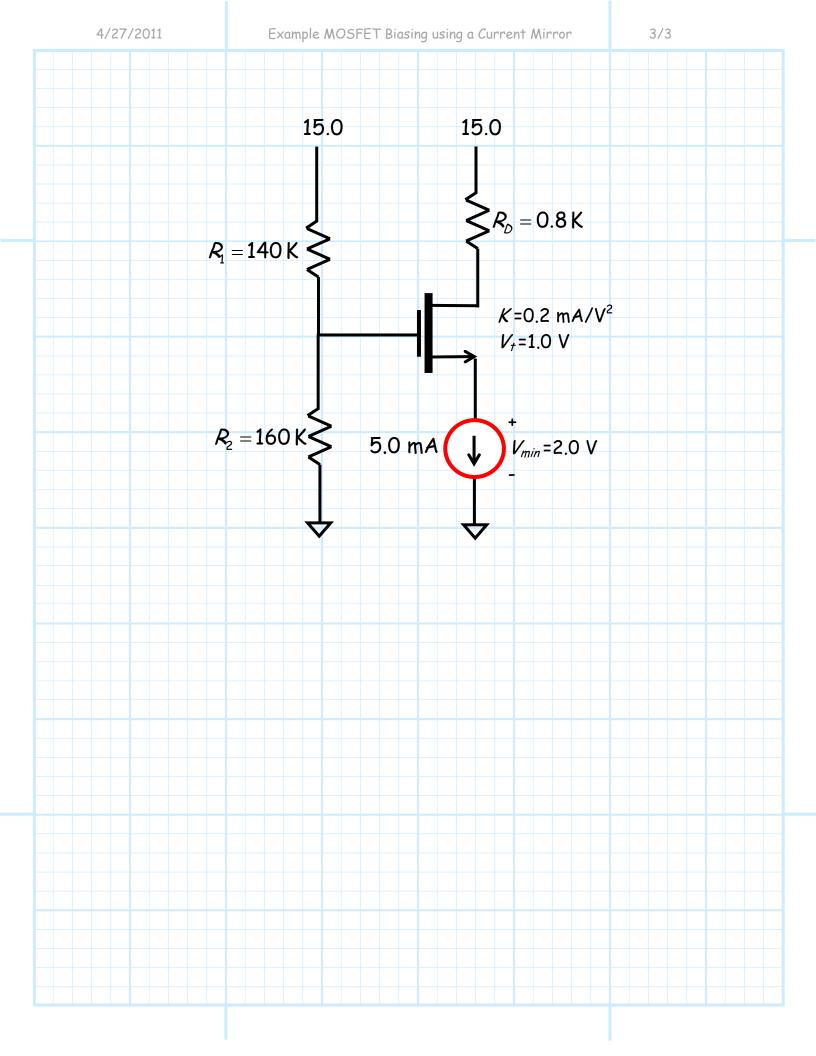

Let's determine the proper resistor values to DC bias this MOSFET. The current source is 5.0 mA and has a minimum voltage of 2.0 Volts in order to operate properly

Assuming that we want the DC source voltage to be the minimum value of  $V_s = 2.0$ , we nee for the DC gate voltage to be:

$V_{G} = V_{GS} + V_{S}$ = 6.0 + 2.0 = 8.0 V Thus, we need to select resistors  $R_1$  and  $R_2$  so that:

$$V_G = 8.0 = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$$

or in other words, we want:

$$\left(\frac{R_2}{R_1+R_2}\right) = \frac{8.0}{15.0}$$

Since we can make  $R_1$  and  $R_2$  large, let's assume that we want:

$$R_1 + R_2 = 300 \, \text{K}$$

So that  $R_1 = 140 \text{ K}\Omega$  and  $R_2 = 160 \text{ K}\Omega$ .

Finally, we want the DC drain voltage to be:

$$V_{b} = \frac{V_{DD} + (V_{G} - V_{f})}{2}$$

$$= \frac{15.0 + (8.0 - 1.0)}{2}$$

$$= 11.0 \text{ V}$$

So that the resistor  $R_D$  is:

$$R_{D} = \frac{V_{DD} - V_{D}}{I_{D}}$$

$$= \frac{15.0 - 11.0}{5.0}$$

$$= 0.8 \text{ K}\Omega$$