## ADS Overview –Part 2

If you have closed ADS, re-open ADS by running the following menu command: Start->Programs->Advanced Design System 2002C->Advanced Design System.

Then open your project by clicking on

Close all windows by choosing File->Close All. Then open a new design by choosing File->New Design. Set the settings as you did in the previous tutorial, only name the design TDR\_Simulation. Choose "OK" when you are done.

| New Design                                                                                                  |                      | ×                   |

|-------------------------------------------------------------------------------------------------------------|----------------------|---------------------|

| Name<br>TDR_Simulation                                                                                      |                      |                     |

| Type of Network                                                                                             |                      |                     |

| Analog/RF Network                                                                                           |                      |                     |

| C Current Window                                                                                            | New Schematic Window | O New Layout Window |

| Schematic Design Templa                                                                                     | es (Optional)        |                     |

| BJT_curve_tracer<br>ConvPulseRespT<br>ConvStepRespT<br>DC_BJT_T<br>DC_FET_T<br>DC_Sweep<br>FET_curve_tracer |                      |                     |

|                                                                                                             |                      |                     |

|                                                                                                             |                      |                     |

Figure 1: New design for TDR Simulation

- **3.** Add the following components to your design as shown in Figure 2 below. Set the components parameters as shown in the figure.

- a. "Lumped-Components: Capacitor (C)" (rotate component with Ctrl-r)

- b. "Lumped-Components: Resistor (R)"

- c. "Source-Time Domain: Voltage Step (VtStep)"

- d. "TLines-Ideal: Ideal Transmission Line (TLIN)"

- e. "Simulation-Transient: Transient simulation controller (Trans)"

- f. Ground from tool bar.

This setup is similar to what we did in the time domain reflectometry lab. The voltage source is a unit step function which turns on at time = 0 [ns] and rises to 1 [V] instantly. This voltage propagates down the transmission line TLIN, but is split in half because of the voltage division that occurs between generator resistance RG and the characteristic impedance Z of the transmission line. The initial voltage wave is shorted through the capacitor and so the reflected wave completely cancels the forward wave. Then as the capacitor becomes an open circuit the reflected wave transitions from -0.5 [V] to 0.5 [V]. We will look at the voltages at the output of the generator and across the load. Label these nodes as shown in the figure. To label a

node, click on . This opens the dialogue box shown in Figure 3 below. Type in the label VG and click on the wire between R1 and TL1. Type in the label VC and click on the wire between TL1 and C1. To remove a node label, you can erase the node name in the dialogue box and then click on the wire **or** select the wire and choose **Edit->Wire/Pin Label->Remove Wire/Pin Label**.

|                                            |      | · · · · | <u>مخ</u> ــــــ |     |     |          |       |     |                      | ·         | · · |

|--------------------------------------------|------|---------|------------------|-----|-----|----------|-------|-----|----------------------|-----------|-----|

|                                            | · ·  | · R     | • • • •          | VG  | VG  | TLIN     | ·VC   | • • |                      | •         | • • |

| · · · · VtStép · · · · ↓                   | 1 ·  | 1 1 R1  |                  | • • | • • | TL1      |       | • • | 1 1                  | ·         | • • |

| in the SRC1 in the                         | L, 🐇 | · ⊢ R=  | 50·Ohm           | • • | • • | Z=50.010 | Dhm 👘 | • • | VC                   | ·         | · · |

| ····· Viow=0.∨····(/                       | t).  |         | • •              | • • | · · | E=720    | • •   | • • | ⊥∶                   | ·         | · · |

| ⊻high=1.∨<br>Deleu=0.peee                  | Γ÷.  |         | • •              | • • | · · | F=1 GH:  | z · · | • • | $\mathbf{T}_{a}^{c}$ |           | · · |

| Delay=0 nsec -<br>Rise=0 nsec              | · ·  |         |                  | • • | · · |          | • •   | • • | łč                   | ,<br>=110 | ÖpË |

|                                            | •    |         |                  |     | · · |          |       |     | 1.1                  |           | 1.1 |

|                                            | · ·  |         |                  |     |     |          |       |     | - ·                  | ·         | · · |

| · · · · · · · · ·                          |      |         | • •              | • • | · · |          |       | • • |                      | •         | · · |

| TRANSIENT                                  |      |         | · ·              | · · | · · |          |       | • • | 1                    | ·         | · · |

|                                            |      |         | • •              | · · | · · |          |       | • • | = .                  | ·         | · · |

| Tran                                       |      |         |                  | • • | · · |          | • •   | • • | • •                  | ·         | · · |

| . Tran1                                    |      |         | • •              | • • | · · |          | • •   | • • | • •                  | ·         | · · |

| StopTime=60.0 nsec<br>MaxTimeStep=0.1 nsec |      |         |                  | • • | · · |          | • •   | • • | • •                  | •         | • • |

|                                            |      |         |                  |     |     |          | • •   |     | • •                  |           |     |

Figure 2: TDR simulation

| Wire/Pin Label:2                                                                                                                                                                         | ×                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Wire/Pin Label                                                                                                                                                                           |                       |

| VG                                                                                                                                                                                       |                       |

| Enter wire label and click the wire or p                                                                                                                                                 | pin                   |

| To create a bus or bundle, use the fol<br>Bus - basename <start:stop[:incr]> E<br/>Tapped wire - basename<index> E<br/>Bundle - wire_label bus,wire_label bu</index></start:stop[:incr]> | ix: A<0:3><br>x: A<0> |

| Close                                                                                                                                                                                    | Help                  |

Figure 3:Adding node names

**4.** Setup your simulation by choosing **Simulate->Setup Simulation**. Set the settings as shown in Figure 4 below. Click on "Apply" to save the settings and then "Cancel" to close the dialogue box.

| Simulation Setup:2                          | × |

|---------------------------------------------|---|

| Setup Single Parallel                       |   |

|                                             |   |

| Dataset                                     |   |

| TDR_Simulation Browse                       |   |

|                                             |   |

| - Data Display                              |   |

| TDR_Simulation Browse                       |   |

| Open Data Display when simulation completes |   |

|                                             |   |

|                                             |   |

| Simulation Mode                             |   |

| <ul> <li>Single Host</li> </ul>             |   |

| C Parallel Hosts                            |   |

| Simulate Apply Cancel Help                  |   |

Figure 4: Simulation setup for TDR simulation

**5.** Now simulate your design by typing F7 or choosing **Simulate->Simulate**. Wait until the data display window opens as shown in Figure 5 below. The data that is

generated from a simulation set is called a data set. The viewer that we use for a dataset is called the data display. We can control where the data is stored and we can control which data display is connected to the schematic. Both the data set and the data display can be saved in separate files. In the data display window, the data display name shows up in the title bar. The default data set of the window is circled in red below. Both of these default to the name we chose for our schematic, but do not have to be the same name.

Figure 5: Data display window for TDR simulation

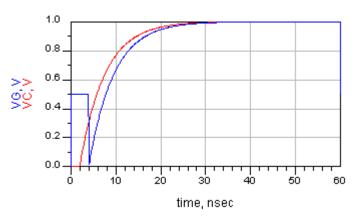

6. Add a rectangular plot by clicking on . Place the rectangular plot on your data display as you would a component. When you do this, a plot traces and attributes window will open. Select VC and click on ">>Add>>". Then select VG and click on ">>Add>>". Then select VG and click on ">>Add>>". We have added two traces: VC versus time and VG versus time. When a transient simulation is done, the assumed x-axis is time. If we had wanted to explicitly set the x and y axes we would choose ">>Add Vs...>>". Your plot attributes window should look like Figure 6 below. Click "OK".

| Plot Traces & Attribute Plot Type Plot Options | s:0                                                    |        | 123 4<br>567 8   | × |

|------------------------------------------------|--------------------------------------------------------|--------|------------------|---|

| Datasets and Equations                         | <u></u>                                                | Traces | 567 8<br>Options |   |

| SRC1.i<br>time<br>tranorder<br>VC<br>VG        | >>Add><br>>>Add Vs.                                    |        |                  |   |

|                                                | < <delete< td=""><td></td><td></td><td></td></delete<> |        |                  |   |

| ОК                                             | Cancel                                                 |        | Help             | — |

Figure 6: Plots traces and attributes window

**7.** You should see the graph in if your schematic and simulation are setup correctly. If it doesn't, double check that each of the steps above.

Figure 7: Transient voltages plot