|

I am a PhD student at the University of Kansas advised by Heechul Yun. My research focuses on time predictability in embedded real-time systems with an emphasis on memory interference. I received my master's degree at the University of Tehran in 2013. There, I worked on approximate arithmetic units for low-power digital signal processing. |

|

|

|

|

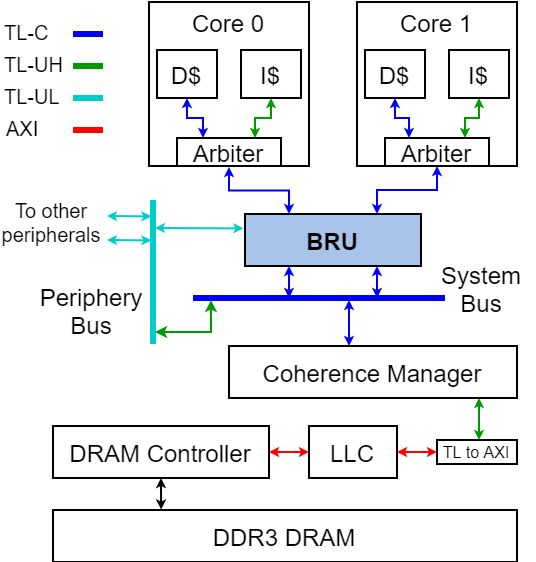

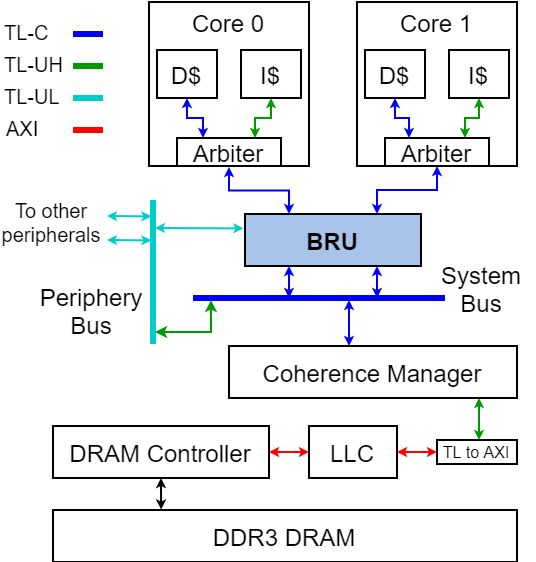

Farzad Farshchi, Qijing Huang, Heechul Yun Real-Time and Embedded Technology and Applications Symposium (RTAS), 2020 BRU-FireSim repo In this paper, we present Bandwidth Regulation Unit (BRU), a drop-in hardware module that enables per-core memory bandwidth regulation at fine-grained time intervals. Additionally, BRU has the ability to regulate the memory access bandwidth of multiple cores collectively to improve the bandwidth utilization. |

|

Jacob Michael Fustos, Farzad Farshchi, Heechul Yun Design Automation Conference (DAC), 2019 slides | repo In this paper, we present SpectreGuard, a novel defense mechanism against Spectre attacks. In our approach, sensitive memory blocks (e.g., secret keys) are marked using simple OS/library API, which are then selectively protected by hardware from Spectre attacks via low-cost micro-architecture extension. |

|

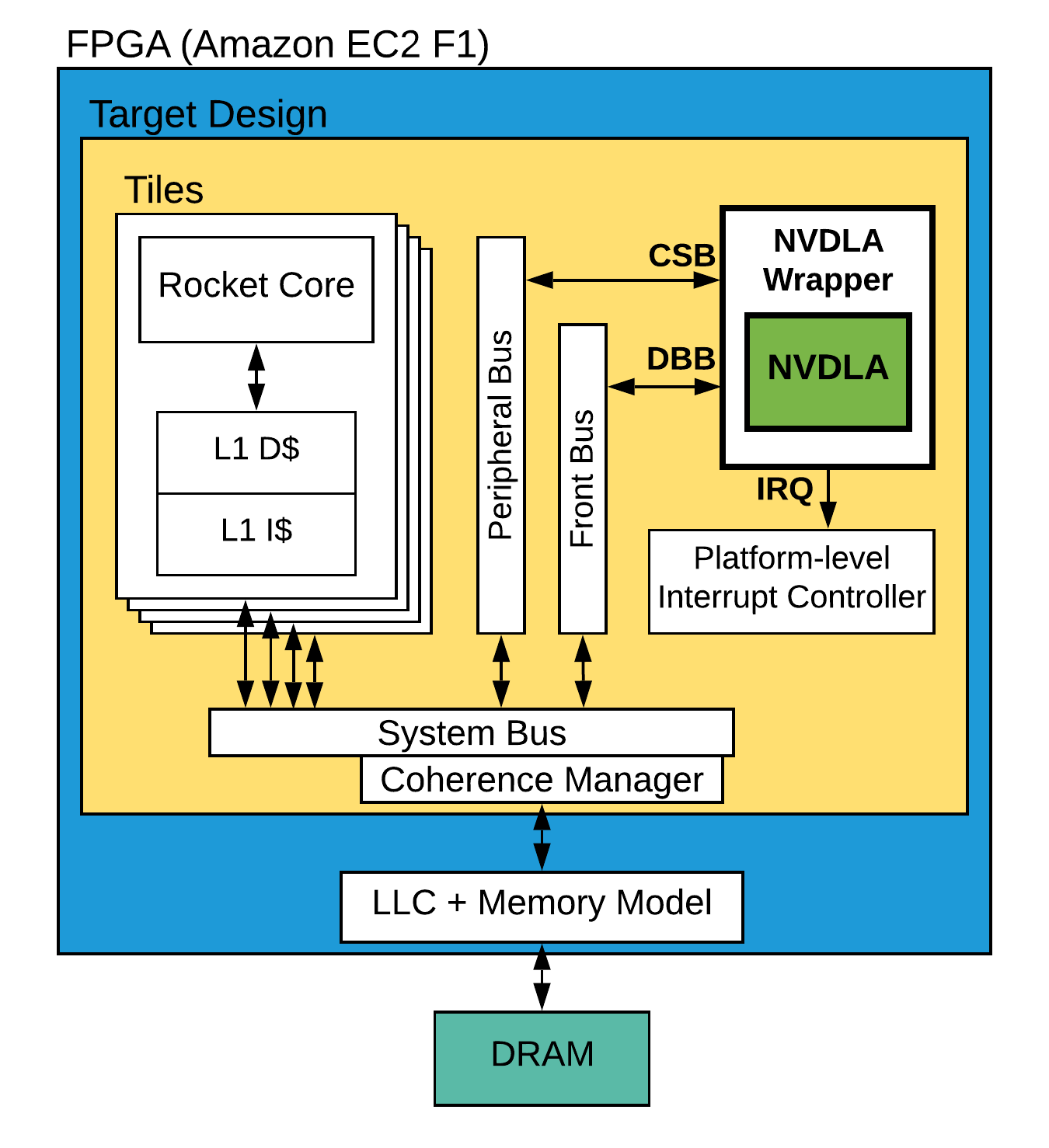

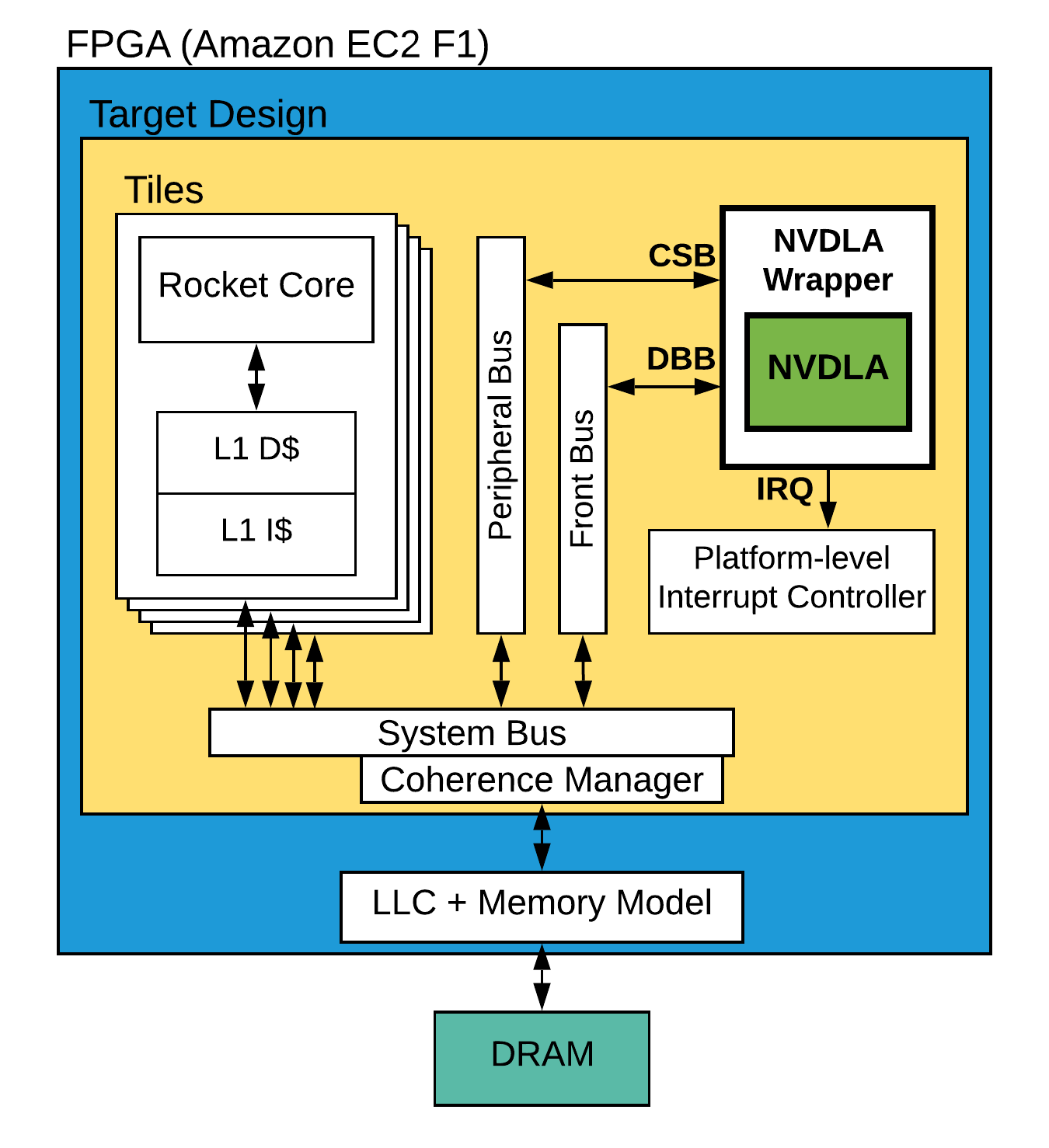

Farzad Farshchi, Qijing Huang, Heechul Yun Energy Efficient Machine Learning and Cognitive Computing for Embedded Applications (EMC2), 2019 slides | arXiv | FireSim-NVDLA repo In this work, we integrate NVDLA into the RISC-V-based Rocket Chip SoC and, with the help of FireSim, we create an FPGA-accelerated cycle-exact simulator which runs on the Amazon EC2 cloud resources. We run YOLOv3 object-detection algorithm on our platfrom for performance evaluation. |

|

|

Farzad Farshchi, Prathap Kumar Valsan, Renato Mancuso, Heechul Yun Euromicro Conference on Real-Time Systems (ECRTS), 2018 slides | arXiv | repo (gem5 and Linux kernel) In this paper, we make a case that a fundamental problem that prevents efficient and predictable real-time computing on multicore is the lack of a proper memory abstraction to express memory criticality. We, therefore, propose a new holistic resource management approach driven by a new memory abstraction, which we call Deterministic Memory. |

|

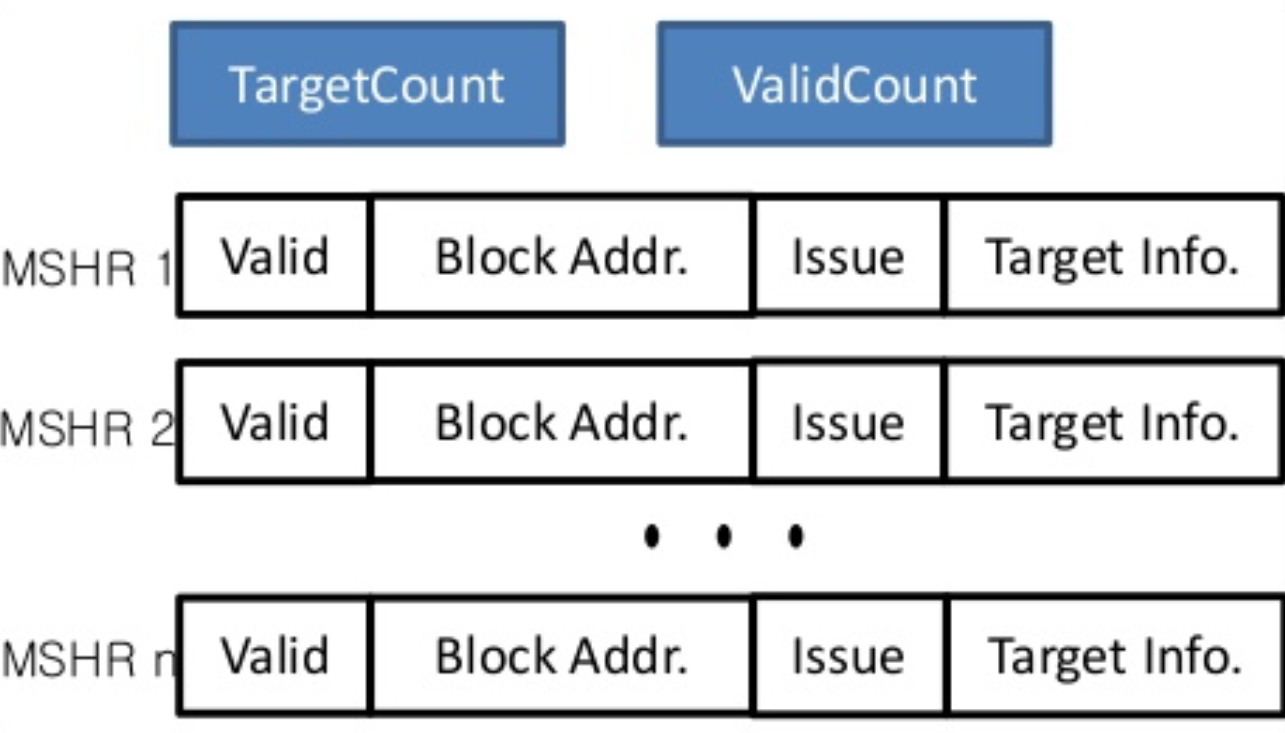

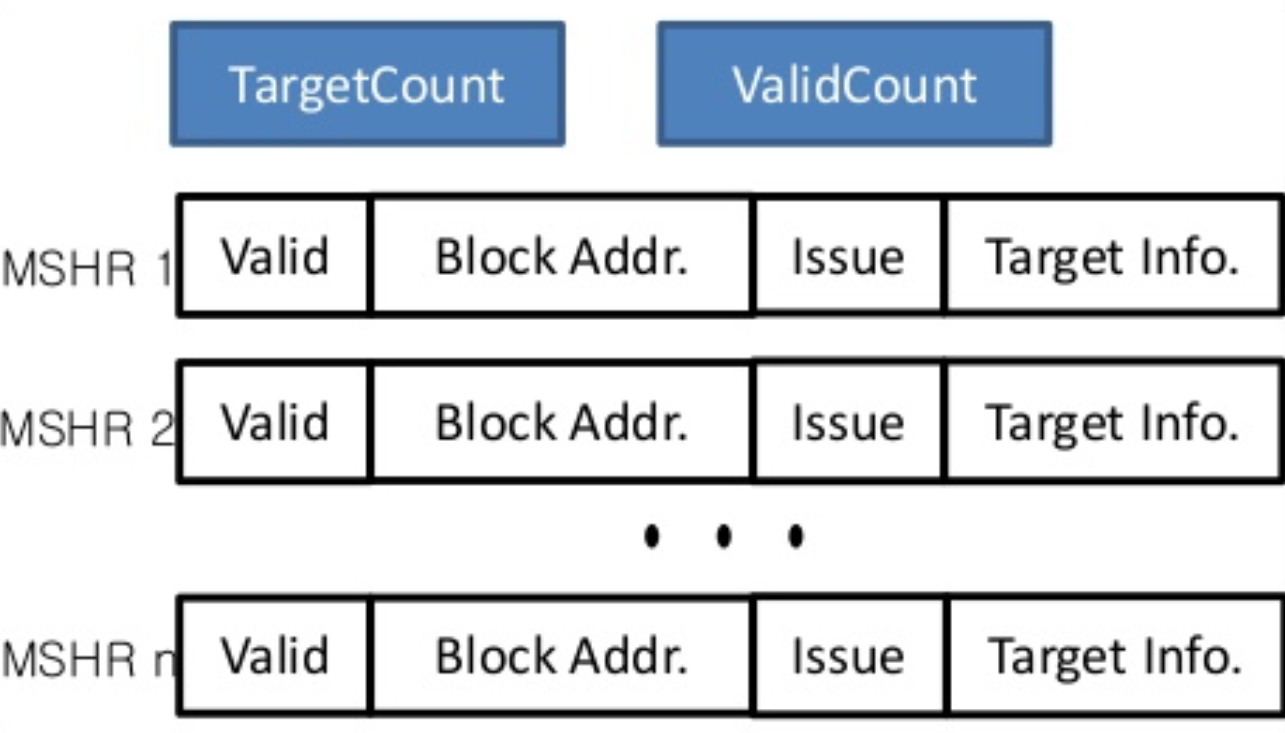

Prathap Kumar Valsan, Heechul Yun, Farzad Farshchi Real-Time and Embedded Technology and Applications Symposium (RTAS), 2016 Extended journal version: Addressing Isolation Challenges of Non-Blocking Caches for Multicore Real-Time Systems. Real-time Systems Journal, 2017. slides | IsolBench benchmark repoIn this paper, we show that cache partitioning does not necessarily ensure predictable cache performance in modern COTS multicore platforms that use non-blocking caches to exploit memory-level-parallelism (MLP). |

|

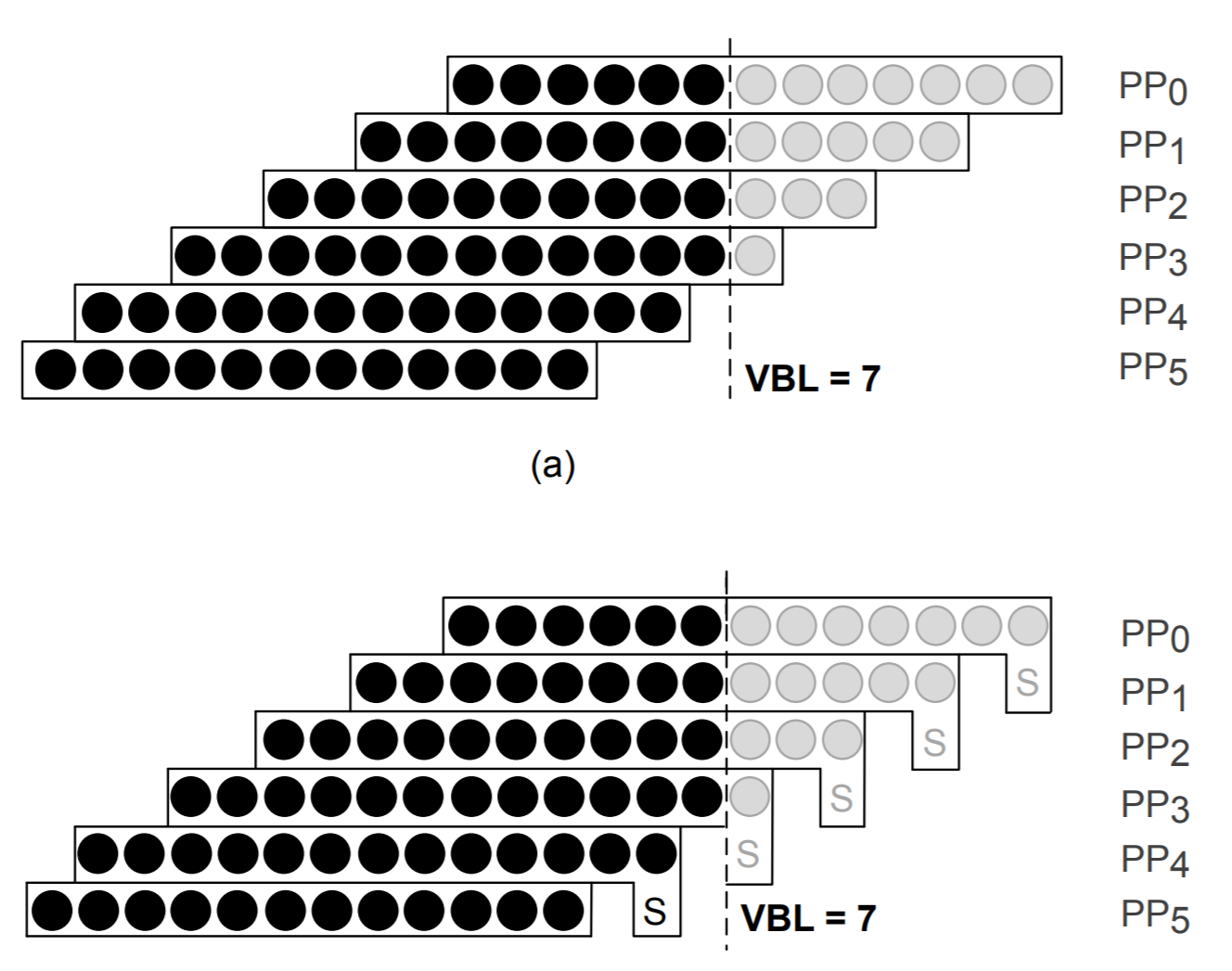

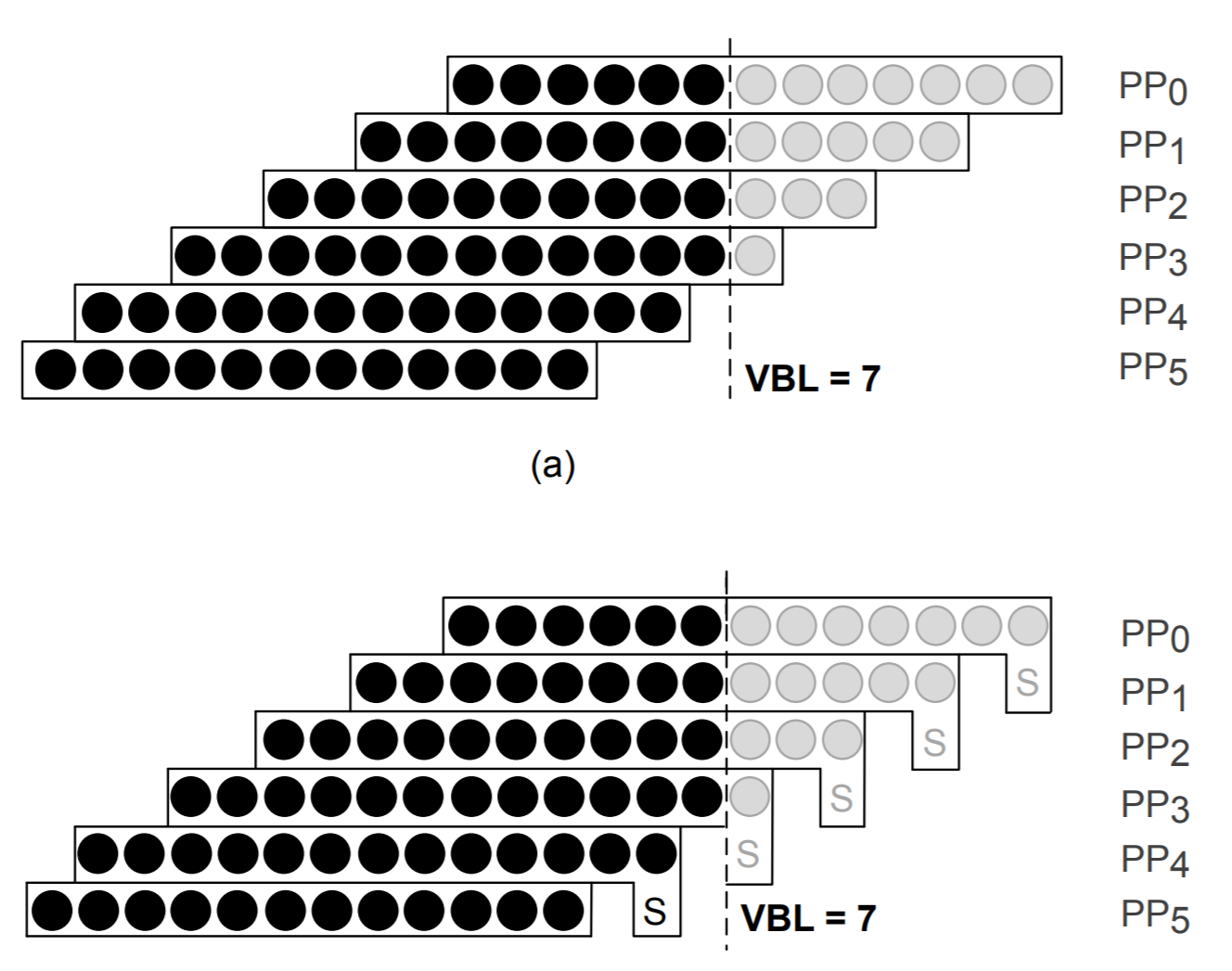

Farzad Farshchi, Muhammad Saeed Abrishami, Sied Mehdi Fakhraie Computer Architecture and Digital Systems (CADS), 2013 repo (synthesizable Verilog and Matlab model) In this paper, we propose a new approximate multiplier which utilizes the Broken-Array Multiplier approximation method on the modified Booth multiplier. Our multiplier reduces the total power consumption up to 58% at the cost of a small decrease in output accuracy. |

|

|

|

SiFive's Freedom RISC-V SoC ported to VCU118 FPGA board

|

|

|

|